[Bình luận] Nhân đồ hoạ Ivy Bridge & Haswell của Intel - Nỗi lo dài cho NVIDIA?

Tháng tư này có thể sẽ đánh dấu sự ra mắt của dòng chip Ivy Bridge (IvB) đến từ Intel, nếu các nguồn tin "râm ran" từ cộng đồng công nghệ là chính xác. Tuy vậy nếu bạn vừa nâng cấp hệ thống lên Sandy Bridge (SnB) từ năm ngoái, liệu có cần thiết quan tâm đến IvB hay không?

Nhưng trước khi du lịch xuyên thời gian tới 2013 để "thăm hỏi" Haswell, chúng ta hãy điểm lại một chút hiện tại về IvB. Về phần CPU (x86), không có quá nhiều thay đổi. Trong nhiều trường hợp, bạn không thấy rõ khác biệt về năng lực điện toán chung (general computing - GP) giữa SnB và IvB. Dù sao theo lộ trình "tick-tock" của Intel, nhân x86 của IvB có thể xem là phiên bản 22nm (tick) của SnB (hiện đang dùng tiến trình 32nm), các thay đổi lớn hứa hẹn sẽ xuất hiện trên Haswell (tock).

Có điều khi năng lực x86 gần như "bão hoà", mọi người lại chú ý hơn về năng lực đồ hoạ (graphics), nhất là đồ hoạ 3D. Mà hiệu năng đồ hoạ của Intel vẫn thường ...bị chê bai. Đây là lý do tại sao x86 của IvB có thể là xem là "tick" so với SnB nhưng nhân IGP (đồ hoạ tích hợp) của nó lại được xem là "tock". Trong khi IGP của SnB chỉ hỗ trợ DirectX (DX) 10.1 của Microsoft (MS), IGP của IvB hỗ trợ đến DX 11, và chi tiết này dẫn tới nhiều thay đổi khá quan trọng.

Khác biệt chính giữa DX 10.1 và DX 11 là hiệu ứng Tessellation (tess). Hiệu ứng này cho phép GPU tự động tạo ra nhiều đường nét đồ hoạ (wireframe) lên đối tượng, thay vì các nhà phát triển game phải tạo thủ công như các thế hệ DX trước. Lợi ích là các game studio có thể tiết kiệm được thời gian thiết kế game hơn so với trước đây (phải tạo nhiều model tùy theo thiết lập của game để "vừa sức" máy). Lẽ dĩ nhiên, nhà sản xuất (NSX) GPU phải bổ sung thêm tính năng này cho con chip của họ và chúng sẽ tốn kha khá silicon. Các GPU hỗ trợ DX 11 buộc phải thêm 3 đơn vị sau : Hull Shader (HS), Domain Shader (DS) và Tessellator. IGP trên IvB cũng vậy.

Một yếu tố khác dẫn đến sự hạn chế năng lực đồ hoạ trên SnB của Intel là vấn đề băng thông nhớ. GT trên SnB / IvB chia sẻ chung giao tiếp nhớ với các nhân x86. Do vậy không tránh khỏi tình trạng "tranh giành" giữa GT và các nhân x86. Bên cạnh đó, trình điều khiển nhớ (IMC) của SnB bị giới hạn ở tốc độ DDR3 1333 MHz dual-channel (tương đương 128-bit). So với các card đồ hoạ tầm trung của AMD hay NVIDIA (giao tiếp nhó 128-bit), con số trên vẫn hết sức khiêm tốn. Lấy ví dụ Radeon HD 5570 dùng bộ nhớ GDDR3 có băng thông nhớ tới 28,8 GB/s, trong khi bộ nhớ DDR3 1333 MHz dual-channel chỉ đạt 10,6 GB/s ! Vì lý do này mà với IvB, các kỹ sư Intel đã bổ sung thêm một bộ đệm L3 Cache riêng (L3$) cho nhân GT. Ngoài ra IMC của IvB cũng tăng mức hỗ trợ DDR3 lên 1600 MHz. Hai nỗ lực này phần nào giảm thiểu vấn đề "tranh chấp" băng thông nhớ tồn tại trên SnB.

Và kết quả ?

Một vài benchmark đầu tiên từ AnandTech (AT) phần nào cho chúng ta cái nhìn sơ lược về hiệu năng đồ hoạ của IvB. Nhân đồ hoạ này có tên thương mại là Intel HD 4000 (đừng nhầm với Radeon HD 4000 của AMD nghen !) nằm trên chip Core i7-3770K. Nó được định hướng để thay thế nhân Intel HD 3000 hiện có trên chip Core i7-2600K. Lưu ý rằng AT sử dụng kit RAM DDR3 4 x 4 GB 1600 MHz : tối đa băng thông nhớ cho IvB.

Crysis Warhead

Dirt 3

Metro

StarCraft II

Skyrim

Nhìn chung, hiệu năng Intel HD 4000 nhỉnh hơn thế hệ cũ 30 ~ 40%, tương ứng với lượng EU tăng 33% (12 lên 16). Trong vài trường hợp, hiệu năng tăng gần 1,5 lần có thể giải thích nhờ sự bổ sung của L3 Cache riêng. Các trường hợp hiệu năng tăng không nhiều có thể bắt nguồn từ vấn đề driver hoặc do game yêu cầu năng lực CPU (x86) nhiều.

Vậy còn Haswell ?

Từ kết quả của IvB, chúng ta có thể nói : "không tệ lắm!".

Dĩ nhiên là điều này chỉ áp dụng được với các hệ thống PC bình dân. Bạn đừng hy vọng có thể đạt chất lượng đồ hoạ tuyệt đỉnh ngay với các khối silicon của Intel. Song, cần bao lâu để Intel có thể thoả mãn thị hiếu người dùng ? Chỉ có một cách duy nhất là nhìn vào lộ trình của Intel.

Như đã nói, Intel sẽ giới thiệu Haswell trong 2013. Cho đến hiện tại vẫn chưa có nhiều thông tin về nó lắm. Dù vậy, như đã nêu, hai trở ngại chính trong đồ hoạ của Intel là lượng EU và băng thông nhớ. Intel vẫn cần khắc phục tiếp điều này và Haswell không là ngoại lệ. Một vài tin đồn cho hay Haswell sẽ có 20 EU, số khác lại nói tới 40 EU ! Dĩ nhiên, chúng ta việc gì phải nghiêng theo phe nào. Điều thú vị là chúng ta có một hình so sánh kích thước các die chip của Intel ở đây (khối chữ nhật màu đen) :

Cả Haswell và IvB đều dùng tiến trình 22nm, còn SnB dùng 32nm và Nehalem là 45nm. Nên không có gì ngạc nhiên khi die IvB và Haswell nhỏ nhất, song die Haswell nhỉnh hơn IvB đôi chút : die IvB kích thước 162 mm2 còn Haswell vào khoảng 185 mm2. Có vẻ như chênh lệch giữa 2 con chip 22nm này chủ yếu nằm ở lượng EU đồ hoạ. Cá nhân tôi cho rằng 20 EU có thể là con số hợp lý, song không loại trừ đấy là 40 EU.

Có điều lượng EU không phải lưu tâm đáng chú ý nhất. Một thông tin tôi cho rằng sẽ thay đổi "căn bản" quan niệm về IGP của Intel là một bộ RAM / cache dùng riêng cho nó.

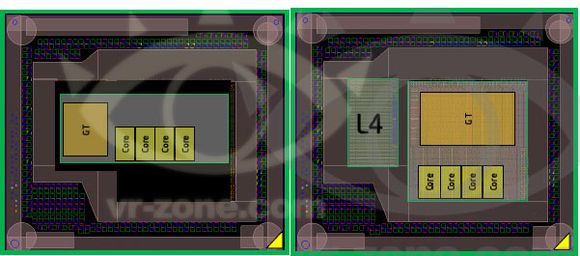

Thiết kế Haswell với giả định có thêm L4 Cache (phải).

Dừng lại một chút ... Ý tưởng này hình như từng áp dụng trên GT của IvB thì phải ? Chính xác ! GT trên IvB có kèm thêm L3 Cache mà chúng ta đã đề cập ở trên. Và Haswell tiếp tục "nâng cấp" ý tưởng này thêm một nấc mới : thêm L4 Cache. Nhưng đừng vội quá khích ! Trước mắt thông tin này chỉ mới là tin đồn. Và chỉ một số phiên bản Haswell (theo tin này) sẽ có L4 Cache, các phiên bản khác chỉ có L3 Cache tương tự IvB. Như hình trên đây.

Dĩ nhiên tin đồn không phải thứ để chúng ta kỳ vọng và chắc chắn, nhưng không phải không có cơ sở. Đơn cử trong quá khứ, chúng ta từng thấy một vài công ty bán dẫn khác thực hiện điều tương tự. Ví dụ IBM có dòng chip Power7 áp dụng eDRAM, hoặc AMD có Side-port memory, đều có cùng bản chất là một bộ nhớ nằm bên ngoài die chip. Kiểu thiết kế này còn được biết với thuật ngữ MCM (multi-chip module).

Intel cũng từng áp dụng MCM cho một vài thiết kế, mà điển hình nhất là thế hệ Pentium D đầu tiên, có bản chất là 2 die Pentium 4 cùng nằm trên 1 tấm PCB. Gần đây hãng này cũng thực hiện một thiết kế MCM tương tự trên dòng chip Atom E6x5C, gồm 1 die Atom liên kết với 1 die Altera FPGA thông qua bus PCIe 2.1. Như vậy không khó để hình dung ra một thiết kế MCM áp dụng cho Haswell gồm 1 die chip và 1 die L4 Cache nằm bên cạnh. Nguồn tin khác phỏng đoán rằng bộ cache này sẽ có dung lượng 64 MB. Bạn có thể cho rằng con số này không lớn, tuy nhiên khi "nói chuyện" trực tiếp với GPU, nó hoàn toàn khác 64 MB DDR3 dùng chung cho toàn hệ thống (system RAM).

Chip Atom E6x5c của Intel là một thiết kế MCM.

Ảnh hưởng của L4 Cache này lên hiệu năng đồ hoạ như thế nào? Hiện tại chúng ta chưa kết luận được gì song điều chắc chắn nếu Intel áp dụng nó thì chi phí sản xuất sẽ tăng thêm đáng kể (bất kể Intel tự sản xuất bộ cache đấy hoặc mua lại của hãng khác đều tiêu tốn một lượng silicon nhất định). Ngoài ra nhìn lại hình ước lượng của VR-Zone, có thể thấy phiên bản kèm L4 Cache sẽ là một thiết kế khác: die chip hình vuông, không phải chữ nhật như bên trái (die Haswell QC gốc).

Và nỗi lo của NVIDIA ...

Bạn có thể tự hỏi: tại sao là NVIDIA mà không phải AMD ? AMD cũng bị Intel cạnh tranh vậy? Lời đáp khá dông dài ...

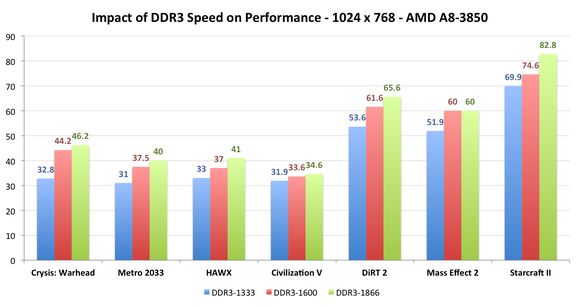

- Về phía AMD, bản thân hãng này đã có Fusion APU, vốn có năng lực đồ hoạ khá mạnh mẽ (bạn có thể xem kết quả benchmark ở trên). Mặc dù hiệu năng x86 không bằng Intel nhưng IGP của AMD hoàn toàn vượt trội. Tất nhiên các vấn đề về IGP mà Intel mắc phải AMD cũng không nằm ngoài. Song APU của AMD khả quan hơn không chỉ ở nhân đồ hoạ mạnh hơn mà băng thông nhớ cũng cao hơn: IMC của chip APU A8 / A10 hỗ trợ bộ nhớ DDR3 tới 1866 MHz, vì vậy mà bạn có thể gia tăng năng lực đồ hoạ trên APU bằng cách ... thay RAM! Như kiểm nghiệm của AT dưới đây cho thấy khác biệt khi dùng DDR3 1333 - 1600 - 1866 MHz với A8-3850.

Trong khi đó IMC trên Sandy Bridge (Intel HD 3000) chỉ tối đa tới 1333 MHz, việc thay RAM không cải thiện chút nào về băng thông nhớ.

Trước mắt hỗ trợ bus RAM cao hơn đem lại ưu thế cho AMD. Nhưng lâu dài thì sao? Không quá khó với AMD để thực hiện một thiết kế MCM tương tự. Vì hãng này hiện đang áp dụng MCM với dòng chip Opteron của họ, bằng cách ghép 2 die Istanbul thành 1 chip Magny-Cours hoặc 2 die Valencia thành 1 chip Interlagos. Nên AMD không phải lo ngại nếu thiết kế L4 Cache của Intel có thật.

- Về phía NVIDIA, câu chuyện hoàn toàn khác. Tuy card chơi game mạnh nhất hiện thời thuộc về NVIDIA, nhưng hãng này không có giải pháp IGP nào tương tự bên Intel và AMD (thực tế Intel đã cắt quyền sản xuất chipset x86 dành cho NVIDIA, NVIDIA cũng không được phép sản xuất CPU x86) nên dù "rất muốn", người khổng lồ đồ hoạ này không có cách nào "chen chân" vào thị trường IGP. Nguyên nhân NVIDIA chuyển hướng sang SoC nền ARM cũng xuất pháp từ đây (bộ phận thiết kế Tegra thực chất là bộ phận thiết kế chipset nForce cũ).

Bên cạnh đó, thị trường card đồ hoạ bình dân đang ngày càng thu hẹp. Một khi IGP của AMD lẫn Intel đủ mạnh để đảm đương hết các game cấu hình thấp, ai sẽ cần mua card rời giá rẻ nữa? Mặc dù chúng ta vẫn luôn trầm trồ trước những chiếc card cao cấp của AMD lẫn NVIDIA, song doanh số của chúng thực sự rất thấp. Một chi tiết thêm cho bạn: 30% doanh thu trước đây của NVIDIA đến từ sản xuất chipset nForce (kèm IGP). Điều này chứng tỏ rằng lợi nhuận đến từ thị trường tầm trung không hề nhỏ. Vậy nếu IGP của IvB và Haswell "đủ xài" cho đa số người dùng, hãng sản xuất laptop nào sẽ cần đến GPU rời của NVIDIA ?

Dẫu sao vẫn còn khá sớm để nói về tương lai. Nhưng với bản thân ban lãnh đạo của NVIDIA, họ sẽ cần hoặc đã có chiến lược mới trước mối đe doạ ngày càng nhiều từ phía Intel ...

NỔI BẬT TRANG CHỦ

Từ viết code đến giám sát: Một công cụ của Microsoft sẽ 'giáng cấp' dân lập trình xuống vai trò 'quản đốc', phải kiểm tra xem AI đang làm gì mỗi ngày

Nghiên cứu của Microsoft cũng chỉ ra cách AutoDev có thể làm thay đổi bộ mặt ngành phát triển phần mềm, bằng cách phân công lại trách nhiệm trong công việc.

'Tim Cook mới chỉ hứa “sẽ đầu tư vào Indonesia”, còn Việt Nam thì Apple đã đầu tư thực sự rồi!'