Giải ngố về bộ nhớ đệm - Memory Cache

Bạn đã bao giờ bị lạc trong một núi các thông số, thuật ngữ kỹ thuật trên máy tính hay điện thoại chưa? Nếu rồi thì nên tham khảo bài viết dưới đây. Lưu ý chống chỉ định với những người không quan tâm, vì nó sẽ rất buồn tẻ đấy.

Trên thực tế, các thiết kế của chip SoC (hệ thống trên một chip) có một vấn đề rất lớn, đó là Bộ nhớ Truy cập Ngẫu nhiên RAM (Random Access Memory) chậm, quá chậm. Vì vậy, người ta phải đưa ra một cách giải quyết khác và nó được gọi là bộ nhớ đệm. Nếu bạn muốn biết về bộ nhớ đệm, hãy đọc bài dưới đây.

Có thể bạn thấy lạ khi nghe nói RAM chậm. Bạn đã từng nghe ổ cứng chậm, ổ CDROM chậm, nhưng bộ nhớ chính thì không thể tin được. Nhưng đó lại là sự thực.

Tại trung tâm của chip SoC là CPU. Nó nắm quyền chi phối tối cao với thiết bị và tốc độ của nó đòi hỏi phải rất cao. Một CPU trung bình của di động có xung nhịp từ 1,5 GHz đến khoảng 2,2 GHz. Trong khi đó, xung nhịp trung bình của module RAM chỉ khoảng 200 MHz. Vậy điều đó nghĩa là thanh RAM trung bình chạy ở tốc độ xung nhịp chậm hơn khoảng 10 lần so với CPU. Điều này quả thật như một khoảng thời gian vô tận. Mỗi khi CPU cần cái gì đó từ RAM, nó sẽ phải chờ đợi, chờ đợi và chờ đợi trong khi dữ liệu được nạp.

Đáng lẽ ra thời gian đó CPU có thể làm điều gì đó khác, nhưng không thể vì nó phải chờ đợi.

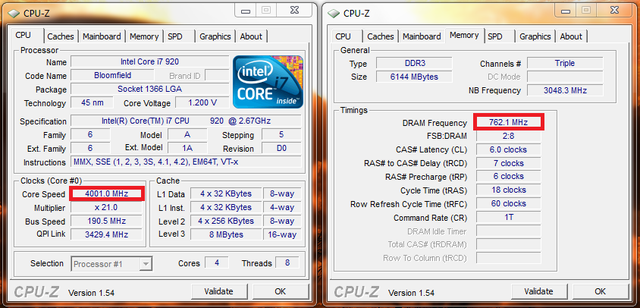

Sự chênh lệch giữa tốc độ xung nhịp của CPU và của RAM.

Như vậy chúng ta đã thấy được mấu chốt của vấn đề. Tuy nhiên, tình hình không thực sự xấu đến mức như vậy, bởi vì những công nghệ như Double-Data-Rate (DDR) RAM có thể gửi đi lượng dữ liệu gấp đôi trong mỗi chu kỳ xung nhịp. Tương tự như vậy, các thông số kỹ thuật như LPDDR3 (Low Power DDR3) cho phép truyền dữ liệu với tốc độ gấp 8 lần so với xung nhịp bên trong. Ngoài ra còn các kỹ thuật được tích hợp bên trong CPU, để đảm bảo dữ liệu sẽ được yêu cầu sớm nhất có thể, trước khi nó thực sự cần đến.

Tại thời điểm của bài viết, các chip SoC mới nhất đang sử dụng LPDDR4 với tốc độ hiệu quả lên đến 1866 MHz, vậy nếu xung nhịp của CPU là 1,8GHz hoặc chậm hơn, bộ nhớ giờ chắc hẳn sẽ đuổi kịp CPU rồi chứ? Không hẳn vậy, vấn đề là các bộ xử lý hiện đại sử dụng 4 đến 8 nhân, vì vậy sẽ không chỉ có một CPU truy cập vào bộ nhớ, mà sẽ có 8 CPU, chúng đều cần dữ liệu, và chúng cần nó càng nhanh càng tốt.

Sự hạn chế hiệu năng này được gọi là nút thắt cổ chai Von Neumann, lấy theo tên của một trong những người chủ chốt phát minh ra máy tính hiện đại ngày nay. Nhược điểm của kiến trúc Von Neumann là nút thắt cổ chai về hiệu năng xuất hiện khi dữ liệu đi qua bị giới hạn do sự khác biệt tương đối về tốc độ giữa CPU và RAM.

Có một số phương pháp để cải thiện tình trạng này và giảm sự khác biệt về hiệu năng, một trong số đó là sử dụng bộ nhớ đệm. Vậy bộ nhớ đệm là gì? Nói một cách đơn giản, nó là một lượng nhỏ của bộ nhớ được đặt trên chip SoC, và chạy cùng tốc độ với CPU. Điều này có nghĩa là CPU không cần phải chờ đợi mỗi khi cần dữ liệu từ bộ nhớ đệm nữa, dữ liệu sẽ được gửi thẳng tới CPU với cùng tốc độ mà CPU hoạt động. Hơn nữa, bộ nhớ đệm được cài đặt trên mỗi một nhân CPU, nên mỗi nhân CPU sẽ có bộ nhớ đệm riêng và sẽ không có bất kỳ tranh chấp nào về việc ai được truy cập vào nó.

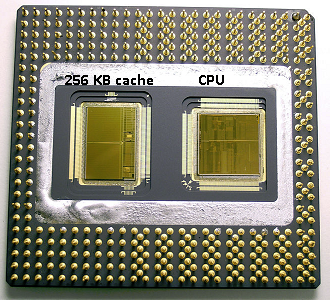

Nếu vậy, sao không làm tất cả bộ nhớ giống như bộ nhớ đệm. Câu trả lời rất đơn giản. Bộ nhớ đệm có thể chạy với tốc độ đó rất đắt. Giá thành (và do những giới hạn của công nghệ chế tạo) là một rào cản thực sự. Đó là lý do tại sao trên di động, lượng bộ nhớ đệm trung bình thường được tính bằng Kilobyte, có thể 32K hay 64K, thay vì hàng Megabyte như thường thấy.

Một CPU với bộ nhớ đệm 256KB.

Vậy giờ mỗi nhân CPU sẽ có vài Kilobyte bộ nhớ siêu nhanh, có thể dùng để lưu bản sao của một phần trên bộ nhớ chính. Nếu bản sao trong vùng đệm thực sự là bộ nhớ mà CPU cần, nó sẽ không cần truy cập vào bộ nhớ chính chậm chạp để lấy dữ liệu nữa. Tất nhiên, thủ thuật là đảm bảo rằng bộ nhớ trên vùng đệm là dữ liệu tốt nhất và được tối ưu, để CPU có thể sử dụng bộ nhớ đệm nhiều hơn và bộ nhớ chính ít hơn.

Do bộ nhớ đệm chỉ có vài Kilobyte nên sẽ có những lúc vùng đệm có đúng nội dung bộ nhớ, còn được biết đến như một “cache hit” (trùng bộ nhớ đệm), và có những lúc không, còn được gọi là “cache miss” (lệch bộ nhớ đệm). Tỷ lệ trùng bộ nhớ đệm càng cao càng tốt.

Phân chia bộ nhớ đệm và hệ thống phân cấp

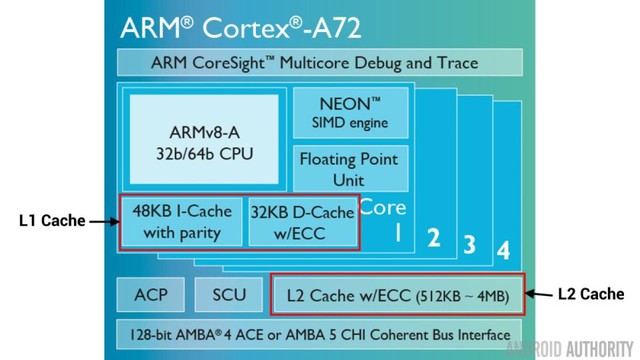

Để giúp cải thiện số lần hit so với miss, có một số kỹ thuật được sử dụng. Một trong số đó là chia bộ nhớ đệm thành hai, một cho các câu lệnh và một cho dữ liệu. Nguyên nhân của việc này là do việc lấp đầy một vùng đệm câu lệnh sẽ dễ hơn nhiều so với dữ liệu, khi câu lệnh tiếp theo được thực thi có thể là câu lệnh kế tiếp trong bộ nhớ. Điều đó cũng có nghĩa là câu lệnh kế tiếp được thực thi, có thể được truy xuất từ vùng đệm câu lệnh trong khi CPU vẫn đang làm việc trên phần bộ nhớ trong vùng đệm dữ liệu. (Do cả hai vùng đệm là độc lập).

Bộ nhớ đệm L1 và L2 trên chíp ARM Cortex-A72.

Một kỹ thuật khác là cải thiện số lần trúng bộ nhớ đệm cache hit là sử dụng hệ thống phân cấp của các bộ nhớ đệm, thường được gọi là bộ nhớ đệm L1 (level 1) và bộ nhớ đệm L2 (level 2). L2 thường có bộ nhớ đệm lớn hơn (thường là 4MB, nhưng có thể còn lớn hơn), tuy nhiên nó lại chậm hơn (nghĩa là chi phí rẻ hơn) và nó được dùng chung bởi tất cả các nhân CPU, làm nó trở thành một bộ nhớ đệm duy nhất cho toàn bộ chip SoC.

Ý tưởng dành cho việc phân cấp này là, nếu dữ liệu đòi hỏi không nằm trên bộ nhớ đệm L1, CPU sẽ cố lấy ra dữ liệu từ bộ nhớ đệm L2, trước khi thử trên bộ nhớ chính. Cho dù L2 chậm hơn L1, nhưng nó vẫn nhanh hơn bộ nhớ chính, và do có kích thước tăng lên nên nó có cơ hội cao hơn để dữ liệu nằm trên đó. Một số thiết kế chíp thậm chí còn sử dụng bộ nhớ đệm L3. Cũng như L2 chậm hơn nhưng lớn hơn L1, L3 lớn hơn nhưng chậm hơn L2. Trên di động, L3 thường không được sử dụng, tuy nhiên, trên các bộ xử lý kiến trúc ARM dùng cho máy chủ (như chíp SoC 24 lõi của Qualcomm sắp ra mắt hay chíp Opteron 1100 của AMD) có tùy chọn bổ sung bộ nhớ đệm L3 32MB.

Tính liên kết

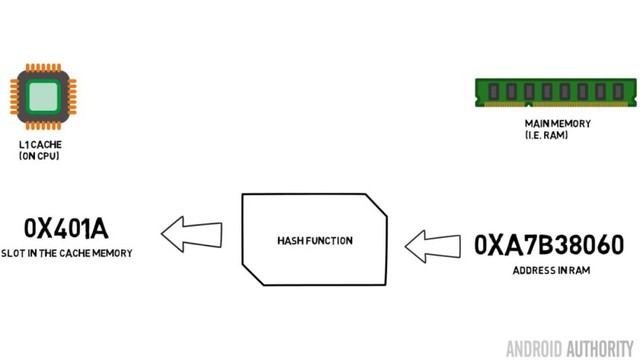

Vẫn còn một mảnh ghép trong bộ xếp hình về bộ nhớ đệm. Đó là làm thế nào CPU biết nội dung từ bộ nhớ chính được lưu ở đâu trên bộ nhớ đệm? Nếu vùng đệm chỉ là một danh sách dài (một bảng tính) của các khe cắm bộ nhớ đệm, CPU cần tìm kiếm trong danh sách đó, từ đầu đến cuối để tìm nội dung nó cần. Tất nhiên, việc đó sẽ chậm hơn là truy xuất những nội dung từ bộ nhớ chính. Vậy để đảm bảo rằng nội dung bộ nhớ có thể được tìm thấy một cách nhanh chóng, một kỹ thuật được gọi là hashing (kỹ thuật băm) cần được sử dụng.

Một hàm băm (hash function) sẽ lấy một giá trị (trong trường hợp này sẽ là địa chỉ của nội dung bộ nhớ, đang được phản chiếu trong bộ nhớ đệm) và tạo ra một giá trị riêng cho nó. Cùng một địa chỉ sẽ luôn tạo ra cùng một giá trị băm. Vì vậy, cách bộ nhớ đệm làm việc là địa chỉ của nội dung bộ nhớ sẽ được băm, và nó đưa ra một câu trả lời cố định, có thể vừa vặn với kích thước của bộ nhớ đệm, (ví dụ như 32K). Do 32K sẽ nhỏ hơn nhiều so với kích thước của RAM, giá trị băm đó cần được lặp, nghĩa là sau 32768 địa chỉ, hash (dữ liệu băm) sẽ cho ra cùng kết quả một lần nữa. Điều này còn được gọi là phép ánh xạ trực tiếp (direct mapping).

Nhược điểm của cách tiếp cận này là khi có nội dung của hai địa chỉ cần được lưu trên bộ nhớ đệm nhưng hai địa chỉ này trả về cùng một khe trên bộ nhớ đệm (ví dụ chúng có cùng giá trị băm). Trong những trường hợp như vậy, chỉ một vị trí trên bộ nhớ đệm có thể được lưu và địa chỉ còn lại sẽ vẫn nằm trên bộ nhớ chính.

Cách tiếp cận khác là sử dụng một hash (giá trị băm) đi thành cặp, vì vậy bất cứ địa chỉ nào cũng có thể là một trong một cặp vị trí trên bộ nhớ đệm, ví dụ như giá trị hash và hash 1. Điều đó nghĩa là hai địa chỉ trước đây có thể bị xung đột, do có cùng giá trị hash, giờ có thể cùng tồn tại. Nhưng giờ để tìm thấy đúng chỗ trên bộ nhớ đệm, CPU cần phải kiểm tra hai vị trí, tuy nhiên điều này vẫn nhanh hơn nhiều so với tìm kiếm trong 32768 địa chỉ! Tên của kỹ thuật ánh xạ này được gọi là liên kết 2 chiều (2-way associative). Cách tiếp cận theo hướng liên kết này có thể mở rộng lên thành 4 chiều, 8 chiều và 16 chiều, tuy nhiên, có những giới hạn của cách tiếp cận này khi hiệu suất tăng thêm không bù đắp được sự phức tạp và chi phí.

Tổng kết

Có một nút thắt cổ chai về hiệu suất trên mọi thiết kế chip SoC, do sự khác biệt về tốc độ giữa bộ nhớ chính và CPU. Nó còn được biết đến dưới tên nút thắt cổ chai Von Neumann và nó tồn tại trên các máy chủ, máy bàn cũng như các thiết bị di động. Một trong những cách để giảm bớt nút thắt cổ chai là sử dụng bộ nhớ đệm, một lượng nhỏ bộ nhớ có hiệu suất cao, được đặt trên con chip với CPU.

Tham khảo Androidauthority

NỔI BẬT TRANG CHỦ

Kênh Facebook của Apple chẳng có 1 post nào, ấy vậy mà lại vừa cập nhật ảnh bìa hé lộ các điểm mới trên iPad?

Bên cạnh hình vẽ cây bút Apple Pencil ám chỉ sẽ có iPad mới cho sự kiện này, nhà Táo còn lặng lẽ "khuyến mãi" thêm 5 bức vẽ khác để fan hâm mộ đồn đoán thêm.

Chính thức: Apple ấn định ngày ra mắt iPad thế hệ mới