Chi tiết về chip 5nm đầu tiên trên thế giới của IBM: 30 tỷ bóng bán dẫn, hiệu năng cao hơn tới 40% so với chip 10nm của Samsung, tiết kiệm 75% năng lượng

Thành quả của sự kết hợp giữa thiết kế bóng bán dẫn mới và công nghệ quang khắc bằng tia cực tím.

Hợp tác với Samsung và GlobalFoundries, IBM mới đây đã trình làng chip silicon 5nm đầu tiên trên thế giới. Điều đặc biệt nhất ở con chip này không phải là hiệu năng hay mật độ bóng bán dẫn vượt trội mà là thiết kế phẳng với các cổng đặt xung quanh bóng bán dẫn gate-all-around GAA cũng như công nghệ quang khắc bằng tia siêu cực tím (extreme ultraviolet – EUV) lần đầu tiên được ứng dụng trong thực tế.

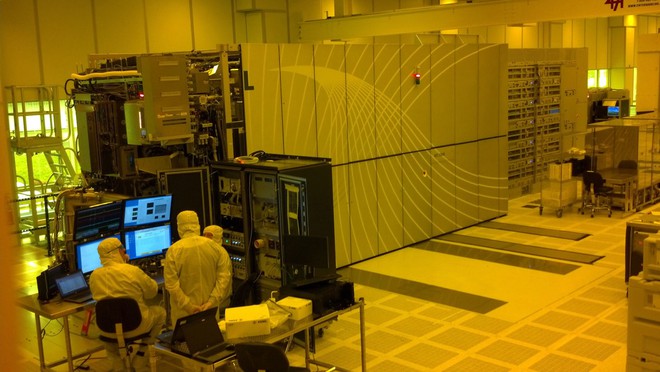

Máy khắc siêu cực tím EUV

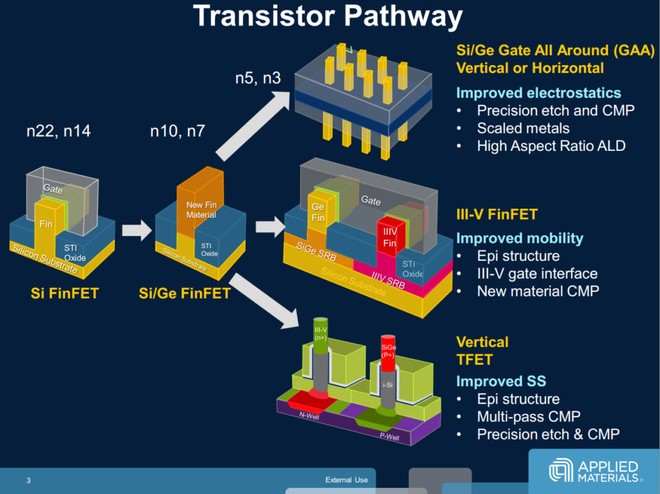

GAAFETs có thể được coi là bước tiến vượt bậc của công nghệ 3 công tri-gate finFETs đang thịnh hành trên các thiết kế chip 22nm hoặc nhỏ hơn. Cũng không có gì lạ khi tri-gate finFETs đang dần trở nên lạc hậu khi áp dụng lên 7nm. GAAFETs sẽ là hướng đi mới cho các nhà sản xuất khi có thể đạt được đến mức 3nm, đặc biệt khi kết hợp với EUV.

Máy vệ sinh tấm wafer

2D, 3D rồi lại 2D

Trước đây, bóng bán dẫn thường được chế tạo bằng cách trải các lớp nguyên liệu lên nhau. Khi các bóng bán dẫn 2D này trở nên ngắn dần, thường là do phải nhét nhiều bóng bán dẫn hơn vào cùng một diện tích, các nhà sản xuất sẽ gặp khó khăn trong việc tạo ra những bóng bán dẫn hoạt động tốt. Cuối cùng, khi các kênh bị thu hẹp quá, sẽ có rất nhiều nguyên tử silicon không thể truyền điện đủ nhanh qua thiết bị.

Khi đó, FinFETs ra đời để giải quyết vấn đề này bằng thiết kế 3 chiều. Với FinFETs, các kênh sẽ không còn là những lớp silicon 2D nữa mà các vây 3D thò lên từ bề mặt vật liệu, giúp nhồi nhét được một thể tích silicon lớn hơn rất nhiều. Các bóng bán dẫn thì ngày càng được thu nhỏ còn các vây 3D này cũng phải được làm mỏng hơn. Bởi vậy, giờ đây các nhà sản xuất chip sẽ cần một loại bóng bán dẫn mới để giữ vững mục tiêu thu nhỏ kích thước.

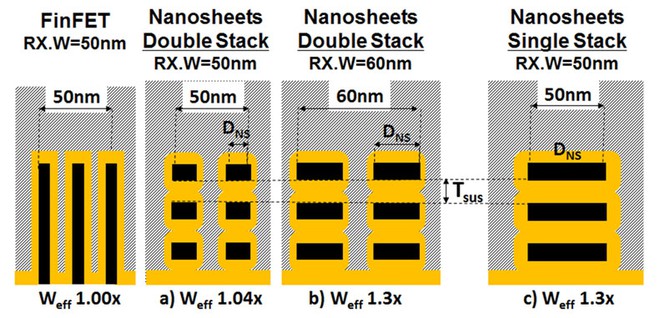

GAAFETs là một dạng thiết kế kiểu 2D nhưng được xây dựng trên kinh nghiệm, máy móc và kĩ thuật được dùng cho finFETs. Có khá nhiều cách để thiết kế GAAFETs nhưng ở màn hợp tác IBM-Samsung-GlobalFoundries, các bóng bán dẫn sẽ được xếp theo chiều ngang. Cách dễ nhất để tưởng tượng về GAAFETs là lấy finFETs rồi xoay 90 độ. Giờ đây, các kênh thay vì là các vây dựng dọc thì giờ chúng sẽ được ép thành chiều ngang. Các vây giờ đây sẽ giống như các dây nanowire (hoặc tấm nanosheet, tùy vào độ rộng) giữa nguồn và bóng bán dẫn.

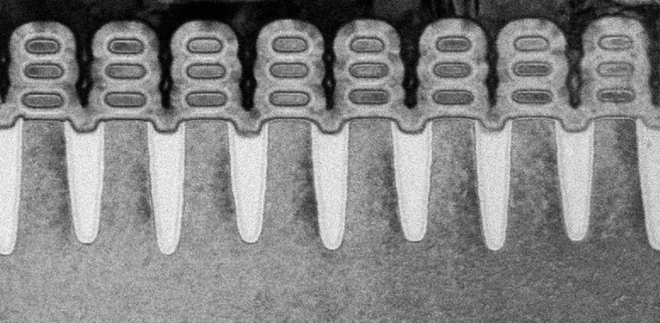

GAAFETs của IBM sẽ bao gồm 3 tấm nanosheet xếp chồng lên nhau với các cổng, thứ bật/tắt các kênh để tạo tín hiệu nhị phân, lấp đầy các khoảng trống. Bởi vậy, các tấm silicon sẽ có một thể tích cổng và kênh khá lớn, giúp GAAFETs trở nên ổn định hơn, hiệu năng tốt hơn cũng như dễ dàng thu nhỏ hơn nữa.

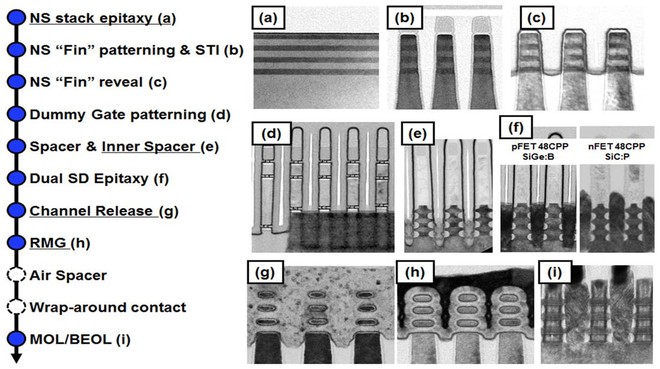

Quá trình sản xuất GAAFETs

Trên phương diện chế tạo, GAAFETs là một tiến trình khá thú vị. Về cơ bản, người ta sẽ đặt các lớp silicon và silicon-germanium (SiGe) xen kẽ. Sau đó, SiGe sẽ được rút ra thông qua một quá trình gọi là “dệt lớp nguyên tử” để lại các khoảng trống giữa các lớp silicon, được gọi là nanosheet. Cuối cùng, các nanosheet đó sẽ được lấp đầy bằng các kim loại chế tạo cổng có trị số k cao.

Sự khác biệt về bề rộng của các kênh truyền dẫn

Một trong những lợi thế của GAAFETs 5nm bởi IBM là việc giảm thiểu được sự phức tạp của việc sắp xếp các thành phần của bóng bán dẫn hay còn gọi là patterning. Sau khi vượt qua công nghệ 28nm, việc sản xuất chip bán dẫn ngày càng trở nên đắt đỏ hơn do cách sắp xếp bóng bán dẫn trở nên phức tạp hơn cùng yêu cầu tăng mật độ. Patterning là một quá trình nhiều công đoạn trong đó bố cục của con chip, thứ xác định vị trí thiết lập của nanosheet và các thành phần khác. Sau đó, các thành phần này sẽ được dệt lại với nhau thông qua quá trình quang khắc. Khi bóng bán dẫn được thu nhỏ, mọi thứ cũng sẽ được thu nhỏ và phức tạp hơn. Khi diện tích silicon được giữ nguyên, để phủ đầy chân đế này, người ta sẽ cần phải pattern nhiều hơn, dẫn đến việc tăng giá thành và thời gian sản xuất các tấm wafer.

Ảnh chụp ngang của các bóng bán dẫn 5nm GAAFETs

Giám đốc nghiên cứu thiết bị silicon của IBM, ông Huiming Bu đã khẳng định rằng chip 5nm là những ứng dụng đầu tiên của công nghệ quang khắc siêu cực tím. Các tia EUV có chiều rộng chỉ 13,5nm, nhỏ hơn cực kì nhiều so với sóng của các máy quang khắc dạng nhúng hiện hành, vốn có chiều rộng lên tới 193nm. EUV thực tế đã được nghiên cứu thành công cách đây 10 năm nhưng chỉ vài tháng gần đây mới được thương mại hóa. Có lẽ thời của tia siêu cực tím đã tới.

Vậy GAAFETs tốt đến đâu?

IBM cho rằng, khi so sánh với chip thương mại 10nm (của Samsung), công nghệ 5nm mới sẽ mang lại hiệu năng cao hơn tới 40% trên cùng một mức điện áp hay nói cách khác là giảm 75% điện năng tiêu thụ. Mật độ bóng bán dẫn cũng tăng vọt khi IBM có thể nhồi tới 30 tỷ bóng bán dẫn vào một con chip diện tích 5mm2, tăng gấp rưỡi so với mức 20 tỷ của chip 7nm.

Hướng đi của các nhà sản xuất chip bán dẫn trong tương tai gần

GAAFETs thực tế cũng không cần đến 5nm mới được áp dụng. Trong ngành công nghiệp bán dẫn, các nhà sản xuất thường có xu hướng cải tiến tiến trình sản xuất và thiết kế bóng bán dẫn hơn là đầu tư hàng tỷ USD để sử dụng một công nghệ mới, chưa ổn định. FinFETs hiện nay đã giúp con người đạt mức 7nm nên việc chạm đến 5nm bằng finFETs cũng không phải là một điều gì đó quá bất khả thi.

Tất nhiên, ở một thời điểm nào đó, người ta sẽ nhận ra rằng thời gian, chi phí và sự phức tạp của việc sản xuát bóng bán dẫn nhỏ hơn sẽ không đáng nữa. Thay vào đó, họ sẽ nghĩ đến việc sản xuất bóng bán dẫn 3D “xịn” bằng cách chồng nhiều đế silicon lên nhau rồi kết nối bằng các công nghệ như xuyên silicon through-silicon vias (TSV). Hiện tại, Intel cũng đã và đang nghiên cứu việc xếp chồng các con chip lên nhau để chuẩn bị cho tiến trình 10nm từ 2015. Công nghệ vẫn đang phát triển từng ngày nên những bóng bán dẫn 3D, 4D có lẽ sẽ chỉ cần vài năm nữa để xuất hiện.

Tham khảo ArsTechnica

NỔI BẬT TRANG CHỦ

Từ viết code đến giám sát: Một công cụ của Microsoft sẽ 'giáng cấp' dân lập trình xuống vai trò 'quản đốc', phải kiểm tra xem AI đang làm gì mỗi ngày

Nghiên cứu của Microsoft cũng chỉ ra cách AutoDev có thể làm thay đổi bộ mặt ngành phát triển phần mềm, bằng cách phân công lại trách nhiệm trong công việc.

'Tim Cook mới chỉ hứa “sẽ đầu tư vào Indonesia”, còn Việt Nam thì Apple đã đầu tư thực sự rồi!'