TSMC - hãng gia công chip lớn nhất thế giới vừa tiết lộ kế hoạch sản xuất chip tiến trình 20nm mới hứa hẹn mang lại các thiết kế ARM, GPU, x86... mới mạnh hơn, tiết kiệm điện hơn so với hiện tại.

Đây là nội dung mà phó chủ tịch kiêm đồng nhiệm CEO của TSMC, Shang-yi Chiang, phát biểu trong thứ tư vừa qua trước báo giới. So với kế hoạch ban đầu, ban lãnh đạo TSMC có một thay đổi khá lớn: node 20nm của hãng này sẽ chỉ có một tiến trình duy nhất, chứ không "phân nhánh" ra nhiều tiến trình "con" như các node 40 và 28nm hiện có. Ngoài ra sau node 20nm, TSMC đang cân nhắc việc đưa ra node 18 hoặc 16nm, trong trường hợp không đáp ứng kịp node 14nm như dự định.

Ban đầu TSMC định đưa ra hai tiến trình 20nm khác nhau, một tối ưu cho các chip hiệu năng cao (tiêu thụ nhiều điện) và một cho các chip tiết kiệm điện (hiệu năng thấp). Hai tiến trình "con" này dự kiến sẽ dùng chung kỹ thuật HKMG (cổng kim loại điện trở cao). Song do một số vấn đề phát sinh trong quá trình R&D (nghiên cứu & phát triển), TSMC đã gom chung hai tiến trình này làm một.

Vấn đề đầu tiên là "chất lượng" của hai tiến trình này không khác biệt nhiều. Do các transistor 20nm có kích thước quá nhỏ và gần đạt tới các giới hạn vật lý cơ bản. Việc thay đổi một vài thông số trong dây chuyền sản xuất không gây ra ảnh hưởng đáng kể.

Vấn đề tiếp theo là sự "phân mảnh" node bán dẫn. Mặc dù các transistor này có kích thước gần tương đương nhau. Nhưng do dây chuyền sản xuất khác nhau, điều này khiến cho sản lượng của từng tiến trình con thấp đi (so với chỉ một tiến trình duy nhất). Sự phân mảnh này cũng là một yếu tố góp phần khiến

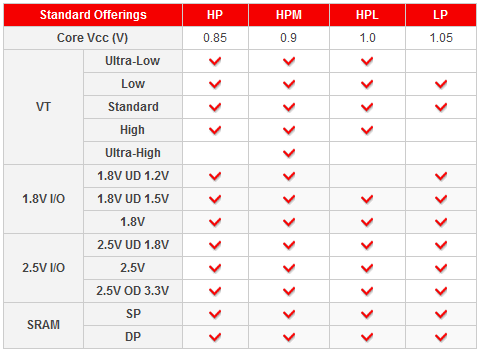

sản lượng node 28nm của TSMC bị sụt giảm (hãng này có đến bốn tiến trình 28nm khác nhau: HP, HPM, HPL, LP).

Node 28nm của TSMC có 4 tiến trình khác nhau.

Do vậy, TSMC quyết định hợp nhất hai tiến trình 20nm ban đầu lại thành một, vừa tiết kiệm chi phí R&D, vừa nâng cao sản lượng chung và góp phần rút ngắn thời gian ra mắt. Đơn vị này dự kiến sẽ bắt đầu sản xuất trên tiến trình 20nm HKMG vào năm sau. Rồi đến 2015, node 14nm là mục tiêu tiếp theo của họ, nhờ "trợ lực" từ kỹ thuật FinFET (mà

Intel đang dùng cho node 22nm).

Lại nói về node 14nm, thực tế các đơn vị bán dẫn (kể cả Intel, IBM, Samsung, GF, TSMC...) vẫn đang trong giai đoạn R&D. Với việc các giới hạn vật lý đang dần tới "ngưỡng", việc thu nhỏ kích thước transistor đang ngày càng khó khăn hơn. Nhiều công ty đang kỳ vọng vào kỹ thuật in litho (lithography) tử ngoại cực mạnh (extreme ultraviolet hay EUV), hoặc in litho chìm (immersion) 193nm để làm ra các chip 14nm. Có điều chưa có gì cho thấy các kỹ thuật trên đã sẵn sàng cho node 14nm vào 2015. Vì vậy mà TSMC lên kế hoạch "dự phòng": phát triển thêm node 18 hoặc 16nm trong trường hợp mốc 2015 cho 14nm không đạt được.

Định luật Moore của Intel xem chừng sắp đến hồi kết?