Intel làm ra chip 22nm như thế nào?

Hôm nay chúng ta sẽ nói một chút về kỹ thuật bán dẫn 22nm của Intel.

Nhanh hơn, mạnh hơn, tiết kiệm điện hơn. Đấy là kim chỉ nam mà giới công nghiệp điện toán (đặc biệt là phần cứng) vẫn luôn tuân theo trong suốt hàng chục năm qua. Nhưng làm sao để đạt được những mục tiêu trên không phải điều đơn giản. May thay, nhờ kỹ thuật bán dẫn và sự sáng tạo của hàng ngàn kỹ sư, những con chip mới vẫn liên tục ra đời dựa trên các dây chuyền sản xuất tiến bộ hơn. Hôm nay chúng ta sẽ nói một chút về kỹ thuật bán dẫn 22nm của Intel.

Transistor, tế bào của chip

Thành phần cơ bản của sinh vật trên hành tinh này là các tế bào. Chip cũng tương tự. Mặc cho có khác biệt về kiến trúc và kích cỡ như nào, mọi con chip mà nhân loại làm ra từ trước đến nay đều dựa trên các transistor, một thiết bị về cơ bản là một công tắc điện. Mục đích của các kỹ sư : có thể bật / tắt / tăng giảm cường độ tín hiệu bất kỳ khi nào họ muốn.

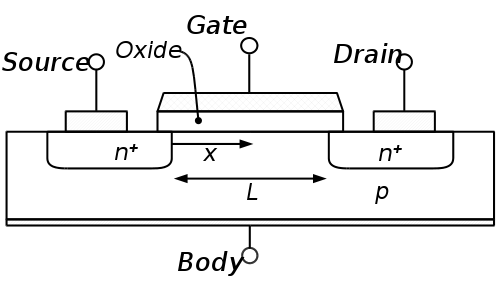

Thế nên việc làm ra chip suy cho cùng là làm ra các transistor. Các transistor được dùng chủ yếu hiện nay trong chip có tên gọi MOSFET, có cấu tạo cơ bản gồm :

- Cực nguồn (source) : nơi dòng điện đi vào

- Cực máng (drain) : nơi dòng điện đi ra

- Cực cổng (gate) : nơi điều khiển việc ra / vào của dòng diện

- Kênh dẫn (channel) : nối giữa nguồn và máng

- Lớp cách điện (oxide) : ngăn dòng điện từ cổng không rò rỉ sang kênh dẫn

Cụm 'FET' trong MOSFET là viết tắt của field-effect transistor, có nghĩa là transistor hiệu-ứng-trường. Thuật ngữ này đồng thời nói lên cách mà transistor hoạt động : khi một điện áp được đặt vào cực cổng, nó sẽ tạo ra một trường điện từ tác động lên kênh dẫn. Tuỳ chủng loại FET (PMOS hay NMOS) mà tác động của trường này sẽ có vai trò đóng / ngắt mạch điện nối giữa 2 cực máng & nguồn.

Bằng cách phối hợp hàng chục, hàng trăm, hàng ngàn ... (và hiện nay lên tới hàng tỷ) transistor, các kỹ sư đã tạo ra những con chip có kiến trúc khác nhau cũng như ứng dụng thay đổi tuỳ mục đích. Số lượng transistor trên một con chip nhìn theo một góc độ nào đấy cũng có thể nói lên sức mạnh chung (khi so với những con chip khác cùng kiến trúc) của chip.

Chính vì số lượng transistor có thể xem như tỷ lệ thuận với sức mạnh chip, nên càng "nhét" được nhiều transistor hơn lên một diện tích cho sẵn sẽ cho ra con chip càng mạnh. Và để đạt được điều này thì kích thước transistor phải thu nhỏ. Đây là lý do tại sao chúng ta thường nghe nói chip 32nm thì tốt hơn 45nm, chip 45nm thì tốt hơn 65nm và cứ thế ... (vì có nhiều transistor hơn).

Intel và transistor 22nm

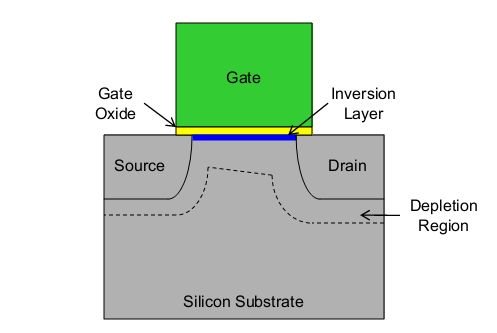

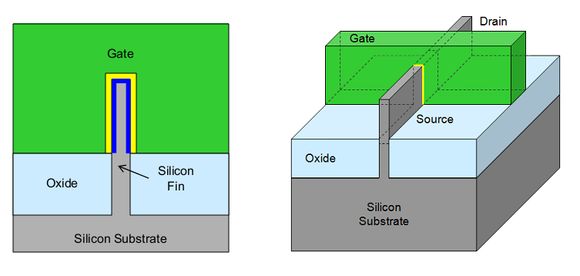

Về căn bản, các transistor bán dẫn trong nhiều năm qua không có thay đổi nhiều. Chúng có kích thước nhỏ hơn, bổ sung thêm một số chất liệu khác để thay đổi hệ số điện trở, hạn chế hiện tượng rò dòng ... nhưng vẫn là các transistor phẳng (planar). Rồi tới tiến trình (node) 22nm, Intel đề nghị ra một dạng transistor mới : đứng (3-D) hoặc nhiều cổng (multi-gate).

3-D transistor về bản chất không lạ lẫm với giới công nghiệp bán dẫn. Đó là FinFET (hoặc các FET dạng "vảy" (fin)) từng được đề ra khá lâu. Song FinFET vẫn chưa được dùng trong các sản phẩm thương mại và Intel là hãng đầu tiên ứng dụng kiểu thiết kế transistor này.

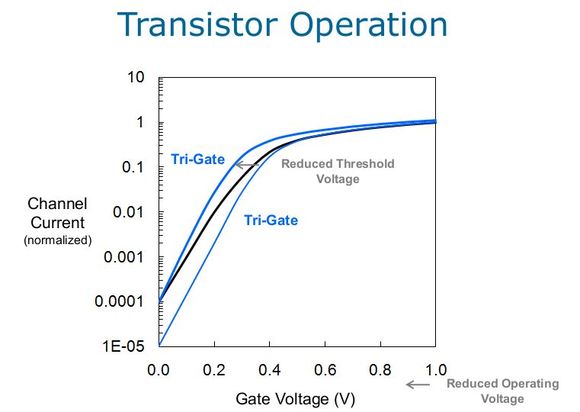

Nhưng tại sao Intel lại thay đổi ? Về phương diện kỹ thuật thì có nhiều thứ để bàn. Ở đây chúng ta chỉ nêu vắn tắt là điện áp ngưỡng (threshold) và điện áp vận hành (operating) của FinFET dễ kiểm soát hơn so với planar. Song thứ gì cũng có 2 mặt : làm FinFET phức tạp và khó khăn nhiều hơn so với planar. Do vậy Intel chưa "vội" chuyển qua FinFET ở các tiến trình trước (65, 45, 32nm ...) mà vẫn dùng planar vì nó vẫn đáp ứng yêu cầu đề ra của Intel.

Có điều với các thiết kế x86 hiệu năng cao của Intel, planar ở node 22nm có vẻ không còn "tốt" nên hãng này chuyển qua FinFET. Mặc dù vậy, giới bán dẫn vẫn tiếp tục dùng planar vì các thiết kế của họ vẫn hoạt động "tốt" với loại transistor này. Do đó bạn đừng cho rằng FinFET là bắt buộc mà "tuỳ nhu cầu mới cần đến hay không".

Tiếp theo chúng ta sẽ đi vào chi tiết từng quá trình làm transistor 22nm của Intel.

Cách Intel làm ra chip 22nm

Các thông tin cơ bản như trên "tạm đủ" để bạn hiểu về cấu tạo chip. Đến đây chúng ta sẽ xem xét cách Intel làm ra từng con chip như nào. Nhìn chung, có 12 bước cả thảy :

Bắt đầu với cát

Như đã nêu, bán dẫn là nguyên liệu chính cho chip hiện nay. Và một loại bán dẫn dc dùng rất phổ biến là Si. Đơn giản vì ... cát rẻ ! Vâng, cát có nhiều và rất rẻ. Đây là một lợi thế về kinh tế.

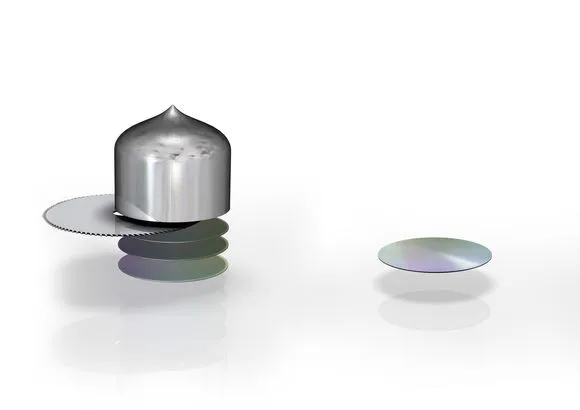

Cát được nấu chảy ở nhiệt độ cao và kết tinh thành từng thỏi lớn (ingot). Tuỳ theo từng dây chuyền sản xuất mà từng thỏi này sẽ được "đặt hàng" với kích thước khác nhau. Các cỡ phổ biến hiện nay là 150mm, 200mm và 300mm. Một yêu cầu khắt khe với từng thỏi silicon trên là chúng phải rất tinh khiết : trung bình chỉ cứ 1 tỷ nguyên tử mới có 1 nguyên tử "lạ" !

Tạo wafer

Ingot không phải thứ Intel dùng, mà là wafer. Đấy là các tấm silicon tròn có bề dày chỉ khoảng 1mm, được cắt ra bằng máy từ các thỏi silicon. Đường kính của ingot cũng chính là đường kính của wafer. Loại wafer tiên tiến nhất hiện nay có đường kính 300mm. Intel đang vận động giới công nghiệp chuyển sang dùng wafer 450mm để tăng cao hiệu quả khai thác trong sản xuất chip. Tuy vậy với bề dày cực mỏng, việc tăng cường kích thước wafer không phải vấn đề đơn giản và giới công nghiệp vẫn đang e ngại trước mong muốn này.

Nhưng người làm ra wafer không phải Intel. Hãng này đặt mua wafer từ các nhà sản xuất khác. Intel chỉ thực sự bắt tay vào sản xuất từ các bước sau.

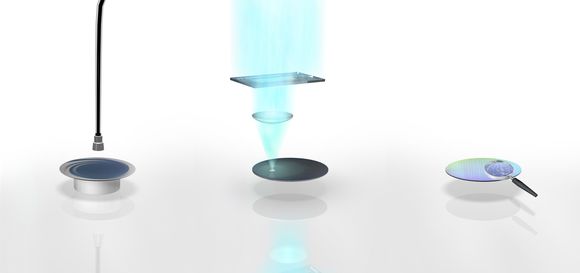

In quang litho

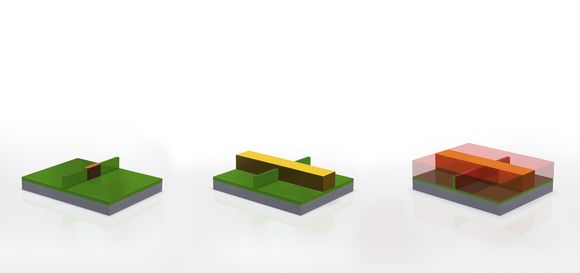

Giống như xây nhà từ bãi đất trống, trước hết bạn phải dựng lên từng thành phần một của ngôi nhà. Đối với việc làm ra transistor, từng thành phần một được tạo ra từ kỹ thuật in litho (lithography). Việc đầu tiên là tấm wafer được phủ một lớp vật liệu ngăn cản ánh sáng (photo resist) (màu xanh dương). Lớp này nhằm bảo vệ lớp silicon bên dưới trong quá trình khắc acid (sẽ nêu sau).

Sau khi được phủ lớp chặn quang, các kỹ sư tiến hành phơi sáng (exposure) tấm wafer dưới ánh sáng tử ngoại (UV), thông qua một lớp mặt nạ (mask) vốn sẽ xác định chi tiết các mạch điện về sau này. Các tia UV có tác dụng biến đổi hoá học lớp chặn quang nằm bên trên khiến chúng bị hoà tan (chỉ khu vực nào bị phơi sáng). Các khu vực hoà tan này sẽ được rửa đi bằng hoá chất và làm lộ ra lớp silicon bên dưới.

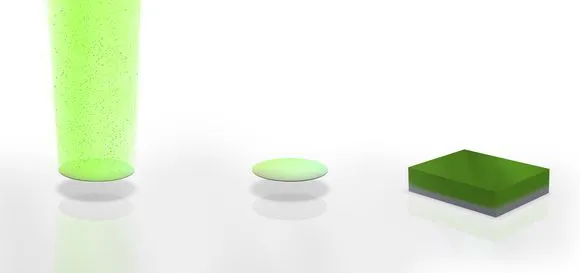

Cấy ion

Tấm wafer sau đấy sẽ được phun các ion có cấu tạo hoá học khác với lớp silicon hiện có. Tuỳ mục đích chế tạo mà các ion này có thể sẽ tạo ra các PMOS hay NMOS, hay lớp cách điện. Chỉ khu vực nào mà lớp chặn quang đã bị loại bỏ ở tiến trình trên thì các ion mới xâm nhập được và nằm lại trên đó.

Tiếp theo, lớp chặn quang còn lại sẽ được "bóc dỡ" nốt nhờ các hoá chất chuyên dụng. Tấm wafer sau giai đoạn này sẽ gồm 2 khu vực chính : silicon "thuần" hoặc silicon "biến tính" (màu lá cây).

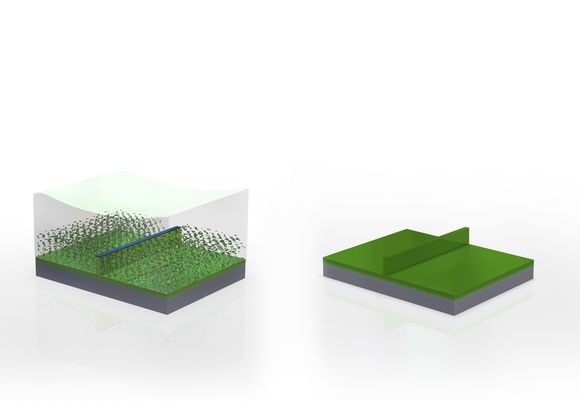

Khắc acid

Dùng lại kỹ thuật in litho đã nêu, các kỹ sư Intel sẽ tạo ra các "vạch" chặn quang để chuẩn bị cho quá trình khắc (hoặc ăn mòn) bằng acid. Lớp chặn quang lúc này có tác dụng ngăn cản việc acid ăn mòn bề mặt silicon nằm dưới. Khu vực nào không được "che chắn" sẽ bị acid "rửa trôi". Thứ chúng ta còn lại đây sau khi lớp chặn quang được tẩy đi nốt là một "vảy mỏng" (fin) sẽ đóng vai trò kênh dẫn về sau này.

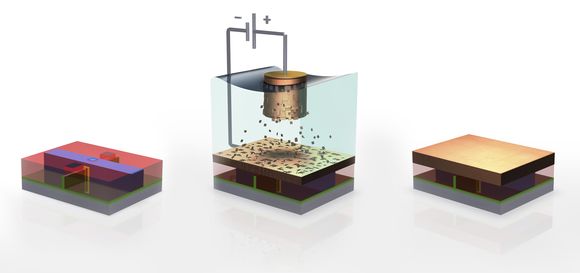

Làm cổng "tạm"

Bắt đầu từ node 32nm và sau này, Intel đề ra kỹ thuật làm cổng tạm (temporary gate). Kỹ thuật này còn được biết dưới cái tên cổng sau (gate-last). Vì trước nay các transistor đều làm ra cổng trước (gate-first) rồi mới đến nguồn & máng. Nhưng Intel cho rằng gate-first gây ra các vấn đề ổn định khi áp dụng kỹ thuật HKMG (cổng kim loại & điện trở cao) nên họ nghĩ ra kỹ thuật gate-last để thay thế.

Gate-last yêu cầu có thêm một bước là làm cổng tạm.

Mượn lại kỹ thuật in litho, các kỹ sư Intel tạo ra một lớp SiO2 mỏng (màu đỏ) đóng vai trò của chiếc cổng giả. Rồi một lớp silicon tinh thể (polycrystal) khác (màu vàng) được phủ lên trên ấy cũng bằng in litho (có thể xem in litho là một kỹ thuật cực kỳ cơ bản trong công nghiệp bán dẫn). Lớp silicon tinh thể này đóng vai trò của một điện cực (electrode) giả.

Sau cùng một lớp SiO2 khác (màu đỏ, trong suốt) được phủ lên trên cùng bọc lấy toàn bộ tấm wafer. Lớp này về sau sẽ trở thành điện môi ngăn cách sự rò điện từ transistor này sang transistor khác.

Tạo cổng HKMG "thật"

Cũng do vấn đề rò điện, từ node 45nm Intel đề ra một kỹ thuật khác là HKMG. Kỹ thuật này về cơ bản thay loại vật liệu làm cổng thành kim loại (metal gate) và lớp oxide cách điện bằng một vật liệu khác có điện trở cao hơn (high-K). Các tiến trình mới sau này, Intel đều dùng HKMG.

Sau khi phủ một lớp SiO2 lên toàn wafer, Intel lại dùng in litho để "bóc" phần SiO2 "thừa" khỏi vị trí mà hãng này muốn đặt chiếc cổng thật (màu xanh dương) vào đấy. Nhưng trước đấy, một lớp vật liệu cách điện (màu vàng) được phủ lên trước để nằm giữa kênh dẫn (màu lá cây) và chiếc cổng (màu xanh dương).

Lắng kim loại

Đến đây thì các công đoạn khó nhất đã gần xong. Chỉ còn việc tạo ra các cực nguồn & máng. Các vị trí này sẽ được tạo ra bởi phương pháp in litho.

Để hoàn tất nguồn & máng, các kỹ sư đặt tấm wafer vào một dung dịch chứa các ion đồng (CuSO4) và dùng kỹ thuật in điện hoá để tạo ra một lớp đồng bám trên wafer : cực dương (anode) sẽ là dung dịch và cực âm (cathode) là tấm wafer.

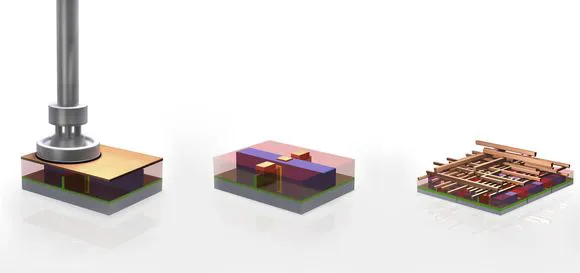

Liên kết các transistor

Sau khi tạo ra lớp đồng, wafer được mài đi để chỉ còn lại 3 vị trí tối cần thiết : cổng, nguồn & máng (màu vàng). Kênh dẫn và lớp cách điện nằm ở phía bên dưới. Vậy là một transistor hoàn chỉnh đã ra đời.

Vấn đề tiếp theo là liên kết các transistor như thế nào. Việc này sẽ lệ thuộc kiến trúc của từng con chip và chúng ta không bàn nhiều tại đây. Thế hệ chip 22nm đầu tiên của Intel sẽ tiếp tục dùng lại kiến trúc Sandy Bridge với một vài cải tiến nhỏ. Thế hệ 22nm kế nữa sẽ dùng kiến trúc mới có tên mã Haswell. Trung bình với một con chip xử lý phức tạp như vầy, Intel cần khoảng 30 lớp transistor khác nhau. Bạn có thể hình dung ra kết cấu của một đô thị về hình ảnh vi mô của chip.

Kiểm định & Loại bỏ chip lỗi

Với một dây chuyền phức tạp gồm nhiều bước như vậy, sai sót là điều khó tránh khỏi. Do đó trong công nghiệp bán dẫn có một khái niệm riêng là hiệu suất (yield). Những kỹ thuật bán dẫn mới thường có hiệu suất rất thấp trong giai đoạn ban đầu. Về sau thì "tay nghề" các kỹ sư được nâng cao nên tỷ lệ này cải thiện theo hướng tốt hơn.

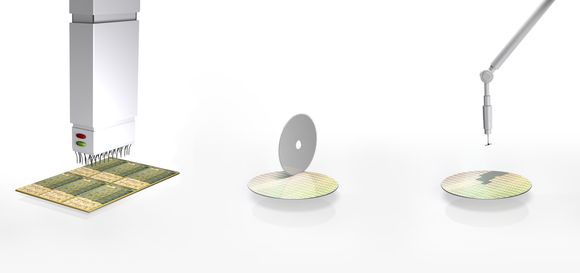

Wafer sau khi hoàn tất các công đoạn trên, sẽ được trải qua một công đoạn là kiểm tra "mềm" (soft test) nhằm xác định die chip nào hoạt động và die nào không. Sau đấy wafer sẽ được cắt ra làm từng die riêng lẻ (như bánh kem) và các die hoạt động được sẽ được lấy ra.

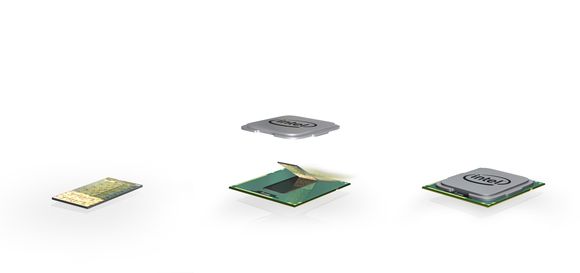

Đóng gói chip

Những con chip thực tế chúng ta thấy là phiên bản hoàn chỉnh, sau khi được kèm thêm bảng mạch PCB và tản nhiệt (vài chip có thể không cần). Nhà máy mà Intel xây dựng tại Việt Nam mấy năm nay sẽ đảm nhiệm vai trò đóng gói này.

Phân loại & Hoàn chỉnh

Trong các die chip hoạt động được, thực tế vẫn có những lỗi nhỏ nhưng không khiến con chip hỏng hoàn toàn. Tuỳ theo loại lỗi mà con chip sẽ được phân loại ra thành model gì. Lấy ví dụ các chip Sandy Bridge 4 nhân thực đều sử dụng cùng một loại die chip. Nhưng vì lỗi ở một vài thành phần (nhân x86, nhân đồ hoạ, bộ nhớ đệm ...) mà chúng được chia thành các model khác nhau.

Sau quá trình này, các chip đã sẵn sàng để Intel tung ra thị trường và "đợi chờ" bạn hoặc ai đó "mang về nhà".

NỔI BẬT TRANG CHỦ

Tính năng AI của điện thoại Huawei gây tranh cãi bởi khả năng lột bỏ quần áo của bất cứ ai

Huawei cho biết đang xem xét để điều chỉnh tính năng này trong tương lai.

Người Nhật mua được CPU Core i7 với giá chỉ 80.000 đồng