Chuyên gia phản bác: Việc tiến trình Intel 18A chỉ đạt "hiệu suất thảm hại" 10% là tin giả

Theo nhiều chuyên gia trong ngành bán dẫn, con số hiệu suất chỉ 10% mà không có ngữ cảnh cụ thể là vô nghĩa.

- ThinkPad X1 Carbon Aura AI ra mắt: Laptop đầu tiên với SSD PCIe 5.0 tốc độ tới 14GB/s, siêu nhẹ chỉ 979g, màn hình OLED, chip Intel Lunar Lake

- Quy trình 18A của Intel rơi vào 'thảm họa': 10 chip ra lò thì 9 bị lỗi, không thể sản xuất hàng loạt, khách hàng lớn tháo chạy?

- Intel từ bỏ chiến lược "không bỏ sót một tấm bán dẫn nào"

- Tiết lộ chấn động: Sự thật đằng sau tuyên bố nghỉ hưu của CEO Intel

- Cổ phiếu Intel tăng mạnh ngay sau khi CEO Pat Gelsinger tuyên bố nghỉ hưu

Trong những ngày gần đây, các bài viết về "tỷ lệ sản xuất thảm hại 10%" của quy trình 18A (Intel 18 Angstrom) đã lan truyền rộng rãi trên mạng xã hội và các phương tiện truyền thông. Tuy nhiên, nhiều chuyên gia trong ngành bán dẫn khẳng định rằng những thông tin này là sai lệch và gây hiểu lầm. Việc đưa ra con số "hiệu suất" sản xuất chip cụ thể mà không có bối cảnh là điều vô nghĩa và cho thấy sự thiếu hiểu biết của nhiều phóng viên và nhà phân tích khi thảo luận về chủ đề này.

Mật độ lỗi mới là yếu tố quan trọng, không phải tỷ lệ sản xuất

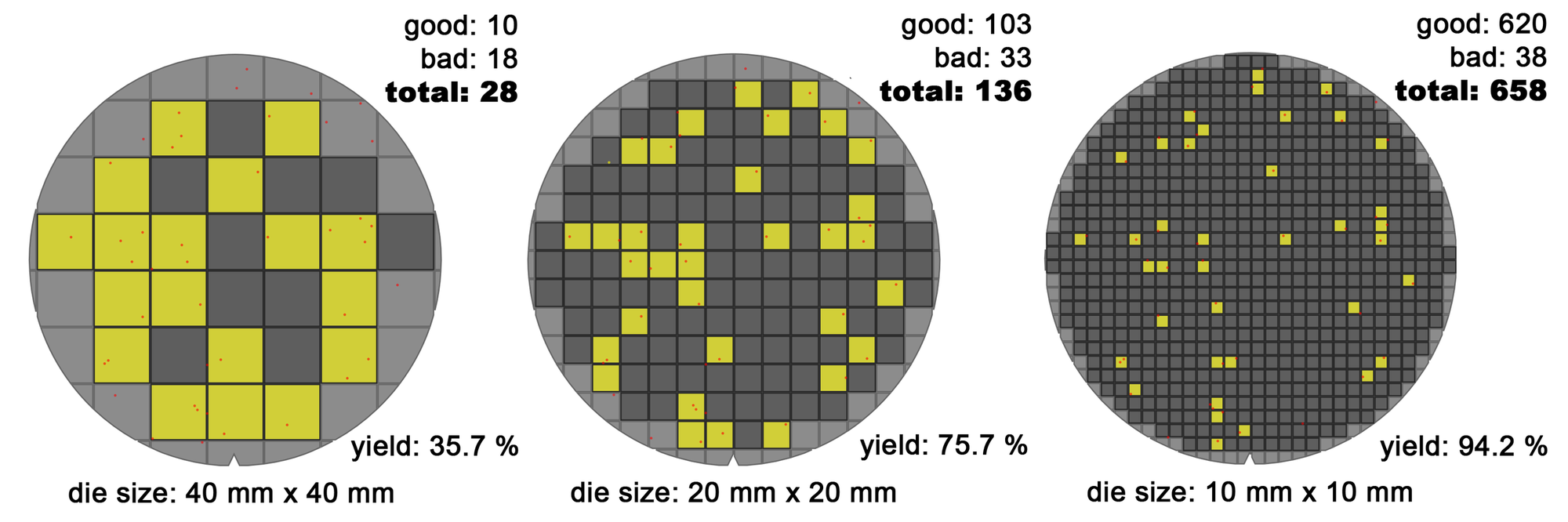

Theo nhiều chuyên gia, kích thước chip và mật độ lỗi mới là điều đáng quan tâm. Tấm wafer silicon có kích thước nhất định và chỉ có thể chứa một số lượng chip nhất định. Kích thước die chip càng lớn, số lượng chip có thể đặt trên một tấm wafer càng ít. Mật độ lỗi của quy trình sản xuất càng cao, số lỗi trên tấm wafer càng nhiều.

Các die chip kích thước khác nhau sẽ có hiệu suất khác nhau với cùng số lượng lỗi

Đối với những chip kích thước nhỏ, do số lượng chip trên mỗi tấm wafer nhiều hơn nên vì vậy, mật độ lỗi ít ảnh hưởng hơn so với chip lớn. Đây cũng là lý do tại sao các quy trình sản xuất mới thường được sử dụng để tạo ra chip nhỏ trước, chẳng hạn như các chip dùng trong smartphone.

Với chip kích thước nhỏ, do số lượng chip sẽ nhiều hơn, nên với cùng số lượng lỗi, tỷ lệ die silicon bị ảnh hưởng sẽ nhỏ hơn so với chip kích thước lớn. Điều này có nghĩa là di chip lớn hơn sẽ chịu tác động của mật độ lỗi lớn hơn. Đây cũng là lý do chính khiến các thiết kế CPU lớn hiện tại đang áp dụng cách tiếp cận thiết kế "chiplet" khi ghép nhiều chip nhỏ hơn với nhau, vì chip nhỏ hơn sẽ có "hiệu suất sản xuất" cao hơn.

Cựu CEO Intel, ông Gel Patsinger, người mới từ chức cách đây không lâu

Hãy nhìn vào ví dụ dưới đây để đơn giản hóa vấn đề. Nếu biết rằng các lỗi sẽ làm hỏng 20 vùng nhỏ trên một tấm wafer silicon (giả định) trong quá trình sản xuất, tỷ lệ sản xuất cho thiết kế chip nhỏ và lớn sẽ như thế nào? Nếu có thiết kế chip nhỏ, có thể đặt 100 chip trên tấm wafer này, chỉ 20 chip bị lỗi và 80 chip còn lại vẫn tốt. Đó là hiệu suất sản xuất 80%. Còn nếu để chế tạo chip kích thước lớn hơn và chỉ có thể đặt 25 chip trên một tấm wafer, sẽ có 20 die chip bị lỗi và 5 die chip còn tốt. Do vậy ta có hiệu suất sản xuất 20%.

Nói một cách đơn giản, con số hiệu suất sản xuất mà không có bối cảnh là vô nghĩa. Bất kỳ con số hiệu suất sản xuất nào cũng có thể được biện minh nếu thiết kế chip đủ nhỏ hoặc đủ lớn.

Nhiều nhà phân tích uy tín gọi đây là tin giả

Patrick Moorhead, một nhà phân tích công nghệ nổi tiếng và được kính trọng, đã gọi việc đưa tin về tỷ lệ lỗi 10% của Intel 18A là "tin giả". Cựu CEO của Intel, Pat Gelsinger, cũng đã cảm ơn ông vì đã làm rõ sự thật và nói rằng ông tự hào về công việc của nhóm phát triển 18A.

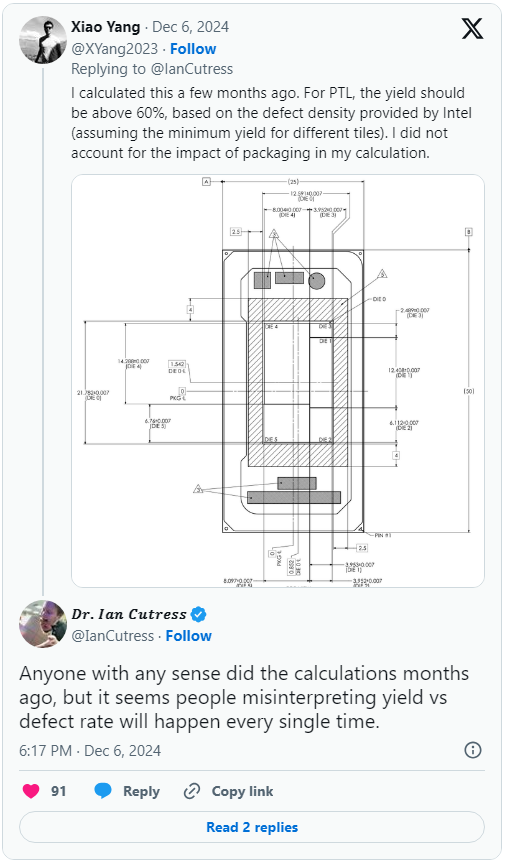

Ông Moorhead cho rằng thông tin về hiệu suất thấp của node Intel 18A là tin giả và cho rằng trên thực tế, Broadcom cũng chưa hề thử nghiệm chip được sản xuất trên tiến trình này. (PDK 1.0 là bộ kit thử nghiệm được Intel cung cấp cho khách hàng sản xuất chip trên tiến trình 18A mới của mình)

Trở lại tháng 9, Intel đã bình luận về mật độ lỗi của quy trình 18A. Họ tuyên bố rằng "mật độ lỗi 18A đã ở D0 <0.40" và "kinh tế học đang ở mức phù hợp để Intel chuyển đổi [sang 18A] ngay bây giờ".

Intel xác nhận rằng họ đã khởi động và khởi chạy các chip dựa trên 18A và "đang đúng tiến độ để ra mắt vào năm 2025". Intel dự định sử dụng quy trình 18A để tạo ra các dòng CPU sắp tới như Panther Lake và Clearwater Forest. Điều đó sẽ không xảy ra nếu tỷ lệ sản xuất "thảm hại ở mức 10%".

Các nhà phân tích đã sử dụng số liệu về mật độ lỗi mà Intel báo cáo để tính toán tỷ lệ sản xuất tiềm năng cho các chip. Ví dụ, một tweet cho biết họ kỳ vọng tỷ lệ sản xuất trên 60% đối với chip Panther Lake (PTL). Điều này giả định rằng Intel chưa cải thiện mật độ lỗi 18A trước khi sản xuất hàng loạt.

Theo tính toán của một số bên khác, với số lượng lỗi trên mỗi tấm wafer được Intel thông báo, hiệu suất sản xuất có thể đạt tới 60% tùy vào loại chip sản xuất

Tại sao tin đồn "tỷ lệ sản xuất thảm hại 10%" cho Intel 18A lại lan truyền?

Hiện tại, có rất nhiều lợi ích tài chính xung quanh Intel và có nhiều lý do khiến mọi người lan truyền tin đồn về tỷ lệ sản xuất kém. Trước hết, chắc chắn có nhiều nhà đầu tư đang bán khống cổ phiếu của Intel. Ngoài ra, một số người muốn thấy Intel thất bại vì những lý do khác. Cũng sẽ có những đối thủ cạnh tranh của Intel Foundry Services không muốn thấy IFS thành công. Đây chỉ là phỏng đoán, nhưng không thiếu những người sẵn sàng cung cấp thông tin sai lệch cho các nguồn tin.

Hy vọng Intel sẽ sớm đưa ra tuyên bố về quy trình 18A. Nếu không, những tin đồn như thế này sẽ tiếp tục lan truyền, gây hoang mang và thiệt hại không đáng có cho Intel cũng như ngành công nghiệp bán dẫn.

NỔI BẬT TRANG CHỦ

Nhà sáng lập TSMC nhận định về Intel: Sẽ tốt hơn nếu không cố chen chân vào mảng sản xuất chip, đáng lẽ nên tập trung vào AI

Morris Chang, nhà sáng lập TSMC, đã thẳng thắn nhận định chiến lược kinh doanh của Intel, cho rằng "Đội Xanh" đáng lẽ không nên bước chân vào lĩnh vực sản xuất chip và thay vào đó nên tập trung vào thị trường AI.

Nửa đêm, Facebook sập trên toàn cầu, Instagram, Threads cũng không thể truy cập