Samsung V-NAND: Lối rẽ mới cho cuộc đua cải thiện chip nhớ NAND

Cấu trúc sắp xếp mới cho phép Samsung quay về với kích thước cell trên 30nm mà vẫn đạt mức dung lượng cao, các hãng khác sẽ nói gì?

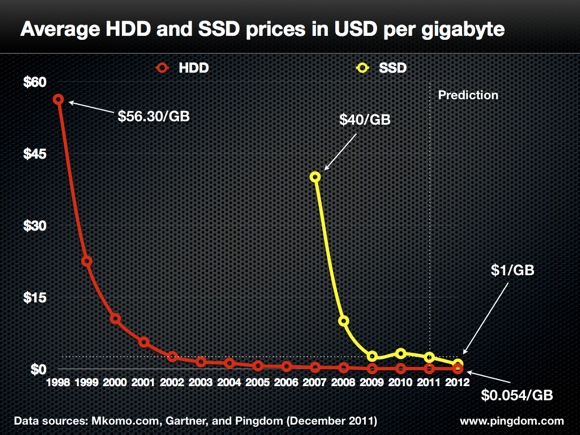

Bắt đầu từ khi Intel ra mắt dòng X25-M của mình hồi 2008, giá thành của SSD cho tới nay vẫn không ngừng giảm xuống, giúp loại ổ cứng này ngày càng đến gần hơn với người tiêu dùng. Nếu như ngày đó ta phải trả tới 600$ cho khoảng 80GB dung lượng lưu trữ trên SSD, thì ngày nay miễn là bạn chịu chi ra ngần đó tiền cho một chiếc ổ cứng - việc kiếm được một model có dung lượng lên tới 1TB từ Samsung hay Micron không phải là quá khó khăn. Câu chuyện đằng sau sự thay đổi nhanh chóng về giá này quanh đi quẩn lại vẫn là về định luật Moore: các bóng bán dẫn ngày càng được thu nhỏ kích thước với giá thành sản xuất rẻ hơn đã mở đường cho việc tích hợp nhiều chip NAND vào cùng một đơn vị diện tích, nhờ thế tăng khả năng lưu trữ.

Hồi kết của cuộc đua “thu nhỏ”

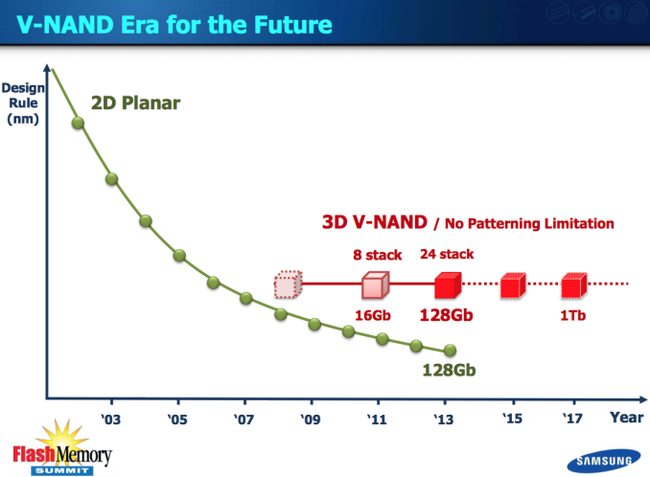

Mặc dù quá trình cải thiện kích thước bóng bán dẫn đồng nghĩa với việc giải quyết vấn đề giá thành trên mỗi bit dung lượng, nó cũng đem đến một vấn đế mới: sụt giảm độ bền và hiệu năng của thiết bị lưu trữ. Cả hai thông số này đều giảm dần trong khi dung lượng tối đa của từng Die (đơn vị cơ bản trên SSD bao gồm khoảng 4000 block bộ nhớ và các thành phần cấp nguồn/điều khiển khác) ngày càng tăng: từ 16Gbit trên các NAND 50nm lên tới 128Gbit trên các mẫu sử dụng công nghệ 16nm. Các mẫu SSD ngày nay chủ yếu giải quyết vấn đề này bằng 2 cách: tận dụng tối đa các công nghệ/thuật toán phát hiện và xử lí lỗi, cũng như áp dụng các biện pháp tính toán/truyền tải song song bất cứ khi nào có thể.

Nguyên nhân của vấn đề cũng tương tự như ta thường nghe trên các công nghệ cho CPU: sự chênh lệch về điện áp quá nhỏ. Chúng ta tự quy định rằng ở điện áp cao thì đấy là bit 1 (hoặc ON), ở điện áp thấp thì đấy là bit 0 (hoặc OFF). Khi nói đến kích thước 14/15/16nm điển hình ngày nay, việc lưu trữ 2bits dữ liệu trên một cell nhớ (các loại MLC NAND điển hình) đồng nghĩa với việc phải đo được chênh lệch giữa chỉ một lượng khá nhỏ các electron. Khi mà kích thước các cell ngày càng giảm, hay như trên các loại TLC NAND (3bit dữ liêu/cell), khó khăn tăng lên gấp bội khi mà “lượng nhỏ electron” này có thể giảm tới mức chỉ còn có thể đếm trên đầu ngón tay.

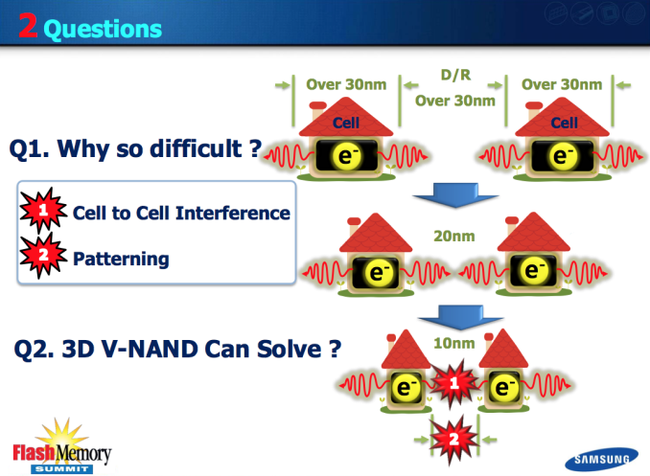

Ngoài việc kích thước các cell nhớ càng được giảm đi, các nhà sản xuất còn muốn tăng số lượng cell trên mỗi đơn vị diện tích bằng cách sắp xếp chúng gần khít nhau hơn, khiến cho việc đo đạc chênh lệch điện thế vốn rất nhỏ này tiến gần đến mức…không thể. Chưa kể khoảng cách gần khiến cho ảnh hưởng qua lại lẫn nhau giữa các cell trở thành một vấn đề khác cần được giải quyết trên các công nghệ từ 20nm trở xuống.

Tóm tắt lại, việc tăng dung lượng lưu trữ và giảm giá thành dựa hoàn toàn vào việc giảm kích thước hay nhồi nhét các bóng bán dẫn sẽ nhanh chóng đi đến hồi kết. Nhiều dự đoán thậm chí cho rằng chúng ta chỉ còn một hoặc hai lần “rút gọn” nữa từ các nhà sản xuất mà thôi. Câu hỏi đặt ra là: sau đó thì sao?

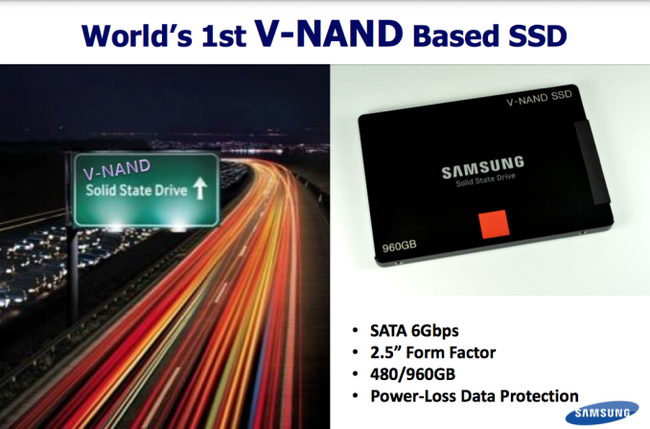

Hồi tháng Tám vừa rồi, Samsung đã đi tiên phong trong việc đưa ra lời giải cho vấn đề này: V-NAND. Trong khi nhiều trang báo liên tục đưa tin về các triển vọng của công nghệ mới từ hãng công nghệ Hàn Quốc, không nhiều nơi dành thời gian giải thích cách mà Samsung vượt qua các rào cản kỹ thuật này.

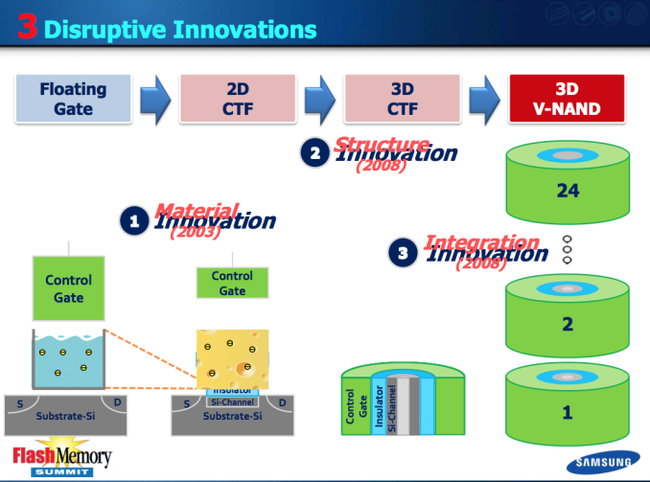

Ba bước cải tiến của Samsung

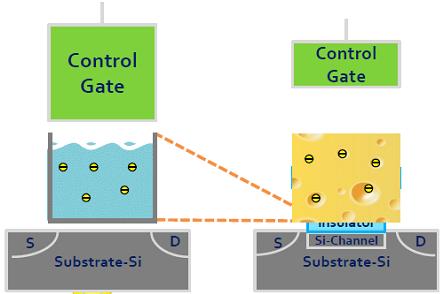

Cấu tạo transitor FGMOS hay Floating-gate MOSFET điển hình trên các SSD ngày nay.

Một transitor điển hình không có khả năng lưu trữ dữ liệu vĩnh viễn, nó chỉ đơn thuần là một công tắc đóng / ngắt dòng điện. Còn trên cấu trúc sử dụng bán dẫn FGMOS hay Floating-gate MOSFET truyền thống của SSD, chiếc cổng trôi (floating-gate) làm từ một vật dẫn chính là nơi lưu trữ trạng thái của các bit dữ liệu ngay cả khi mạch điện đã bị ngắt – cốt lõi khiến FGMOS khác biệt với các thiết kế truyền thống. Đúng theo thiết kế ban đầu floating-gate không được nối dẫn điện với bất cứ thành phần nào khác. Nhưng trong quá trình sử dụng, các sự cố xảy ra với bóng bán dẫn (hay đơn giản là việc thực hiện thao tác ghi liên tục) có thể khiến cho floating-gate bị nối ngắn mạch với các chi tiết khác và khiến điện áp trên đó – cũng chính là dữ liệu của người dùng, bị rút sạch.

Charge Trap Flash - CTF bảo đảm không có sự thất thoát điện áp/electron so với floating-gate.

Tận dụng thiết kế Charge Trap Flash (CTF), về cơ bản Samsung đã loại bỏ hẳn việc sử dụng thiết kế floating-gate bằng vật liệu dẫn điện trước kia. Thay vào đó dữ liệu được lưu trên một lớp cách điện – chính xác hơn là lưu trữ các electron trên một lớp phim silicon nitride. Theo như tiến sĩ ES Jung – trưởng phòng nghiên cứu và phát triển của Samsung – thiết kế floating-gate giống như việc lưu trữ các quả bóng (electron) trong nước, chúng có thể tự do di chuyển và sẽ có lúc lọt đi mất. Còn trong CTF các electron sẽ được giữ chặt trên lớp phim và không thể di chuyển. Việc sử dụng lớp này sẽ tăng đáng kể độ bền của các cell nhớ, cũng như phần nào giảm được kích thước của chúng. Nhưng đó chỉ là một phần của câu chuyện, xét cho cùng CTF cũng vẫn chỉ là một câu chuyện cũ từ 2003.

Ngày nay, Samsung tận dụng các đặc tính của CTF để giải thoát các cell nhớ khỏi cấu trúc phẳng truyền thống. Lớp cách điện nói trên sẽ được bọc quanh các kênh của bóng bán dẫn, trong khi lớp control gate (điều khiển việc ghi dữ liệu lên đó) sẽ nằm ở ngoài cùng. Kiến trúc này, theo như Samsung, tăng đáng kể lượng diện tích có thể được tận dụng để lưu trữ điện áp, đồng nghĩa với việc tăng hiệu năng và độ bền.

Mảnh ghép cuối cùng nằm ở thao tác xếp chồng các cell 3D CTF nói trên lên nhau (xem hình). Do mật độ các cell lúc này được dồn theo chiều dọc, các dây chuyền sản xuất sẽ không còn phải chịu sức ép về kích thước bóng bán dẫn. Thực tế, Samsung cho biết nhờ thiết kế mới giúp tận dụng hiệu quả diện tích sử dụng, hãng này chỉ cần sử dụng kích cỡ trung bình 30-39nm làm nền tảng cho các sản phẩm V-NAND. Bạn đọc có thể xem những hình ảnh minh họa hết sức trực quan từ Samsung về toàn bộ quá trình này trong video dưới đây.

Quay về với kích thước lớn hơn 20nm đồng nghĩa với việc Samsung sẽ tiếp tục thu được lợi thế từ việc các cell không còn gây ảnh hưởng qua lại lẫn nhau, cũng như độ bền tốt hơn. Việc giảm ảnh hưởng này cũng phần nào tăng tốc độ ghi, giảm số lần thực hiện lại của các thao tác đọc/ghi, tương đương với hiệu năng tốt hơn là điện năng tiêu thụ tổng thế thấp hơn. Kết hợp tất cả các yếu tố nói trên lại, ta có được một giải pháp khá hoàn thiện: một chip nhớ V-NAND được quảng cáo có thể hoạt động hiệu quả lên tới 35 ngàn chu kỳ đọc/ghi, gấp hơn 10 lần so với các mẫu MLC NAND thường gặp ngày nay với mức 3000 chu kỳ.

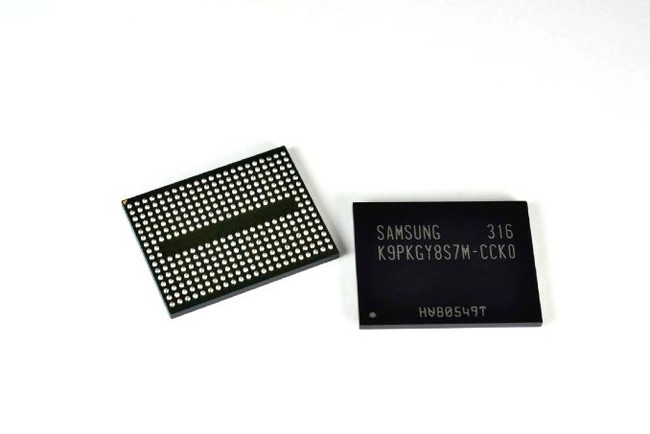

Để chứng minh rằng việc quay về với kích cỡ bóng bán dẫn lớn hơn không hề ảnh hưởng tới mật độ, mới đây Samsung đã giới thiệu thế hệ MLC V-NAND 128Gb của mình. Theo như quảng cáo, mật độ transitor của sản phẩm này lớn gấp đôi so với các mẫu 64Gb 19/20nm, tức gần tương đương với các ổ 128Gb sử dụng bóng 15nm thiết kế và sắp xếp theo dạng truyền thống. Dĩ nhiên kèm theo đó là các lợi thế hơn hẳn về độ bền cũng như hiệu năng.

Câu chuyện của tương lai

Hãng này cũng nhanh chóng tuyên bố việc mình đang thử nghiệm một số sản phẩm chuyên dùng cho doanh nghiệp, đồng nghĩa với việc ta hoàn toàn có thể trông chờ vào các mẫu với dung lượng lớn hơn nhiều so với mức 128Gb. Theo như lộ trình dự định, Samsung đang nuôi tham vọng công bố các mẫu SSD 1Tb dựa trên V-NAND vào khoảng 2017. Và đó là còn chưa đả động gì đến các tiềm năng của TLC V-NAND (3bit/cell). Chừng đó là đủ chứng minh tiềm năng của các công nghệ CTF cũng như 3D NAND là lớn tới đâu. Các hãng sản xuất khác không sớm thì muộn cũng sẽ phải tìm được cách ứng dụng hai giải pháp này lên các sản phẩm của mình, hoặc tìm ra một hướng đi khác thậm chí có nhiều tiềm năng hơn. Cuộc đua càng gay cần, người dùng càng được hưởng lợi.

NỔI BẬT TRANG CHỦ

Tại sao nhân loại lại cần đến máy tính lượng tử, chúng được dùng để làm gì?

Điện toán lượng tử hiện tại vẫn còn cách xa khả năng ứng dụng rộng rãi, nhưng tiềm năng mà nó mang lại là không thể phủ nhận.

Huawei xác nhận ra mắt Mate 70: Dòng smartphone đầu tiên "đoạt tuyệt" hoàn toàn với Android