Như vậy là những con chip Ivy Bridge (IvB) của Intel đã

chính thức ra mắt trên toàn cầu được hơn một tháng. Sử dụng tiến trình 22nm, những con chip này được kỳ vọng sẽ tiết kiệm điện hơn so với đàn anh Sandy Bridge (SnB) 32nm. Tuy nhiên theo nhiều testlab, điều kỳ vọng ấy không diễn ra mà còn bị lật lại: chip IvB thậm chí hao điện hơn cả SnB. Lý do? Chúng ta chưa được rõ. Song theo một vài nghiên cứu từ các hãng thứ ba, nguyên nhân có thể đến từ chính những transistor (

trans) "tri-gate" 22nm mà Intel PR rầm rộ nhiều tháng từ trước khi ra mắt IvB.

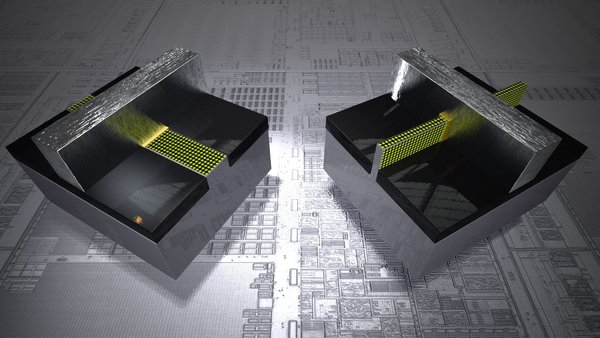

Trans Planar (trái) và Tri-gate (phải).

Nếu bạn chưa hiểu lắm về trans, đặc biệt là trans 22nm "tri-gate" của Intel, hai bài viết sau sẽ hỗ trợ phần nào cho bạn.

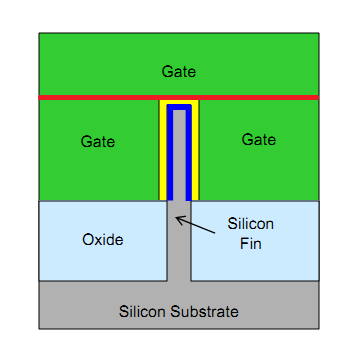

Cụm "tri-gate" mà Intel dùng ở đây mang nghĩa "ba chiếc cổng", như bạn thấy ở hình trên (các cổng nằm ở các góc so với kênh dẫn (channel) có tên silicon fin). Tức theo hiểu biết của giới công nghệ, những tấm vảy (fin) sẽ có dạng vuông chữ nhật. Song thực tế nó lại không như thế.

Ảnh chụp hiển vi cấu tạo trans 22nm của Intel do Chipworks cung cấp.

Một kết quả nghiên cứu do Chipworks công bố gần đây cho thấy: chiếc vảy kia có dạng mũi tên tam giác hơn là một hình chữ nhật. Sử dụng một kính hiển vi truyền điện tử (TEM) - có khả năng nhìn rõ đến... từng nguyên tử, Chipworks thực hiện chụp cắt lớp một con chip IvB của Intel, model Xeon E3-1230 phiên bản cho server. Về bản chất con chip Xeon này không khác gì các phiên bản Core i dùng trên desktop & laptop.

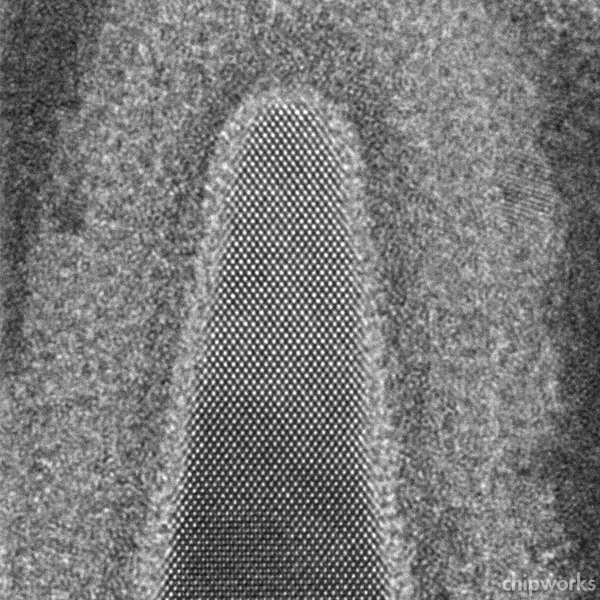

Mô hình 3D về trans 22nm của Intel.

Nhưng bạn thắc mắc: thực ra "vuông" hay "nhọn" thì ảnh hưởng gì? Từ kết quả phân tích của Chipworks, một công ty chuyên về điện tử khác là Gold Standard Simulations (GSS) đã thiết lập một mô hình giả lập 3D về mẫu trans trên. Trong chừng mực nào ấy có vẻ khái niệm "tri-gate" không giống với suy nghĩ của nhiều người cho lắm. Và kết quả như thế nào?

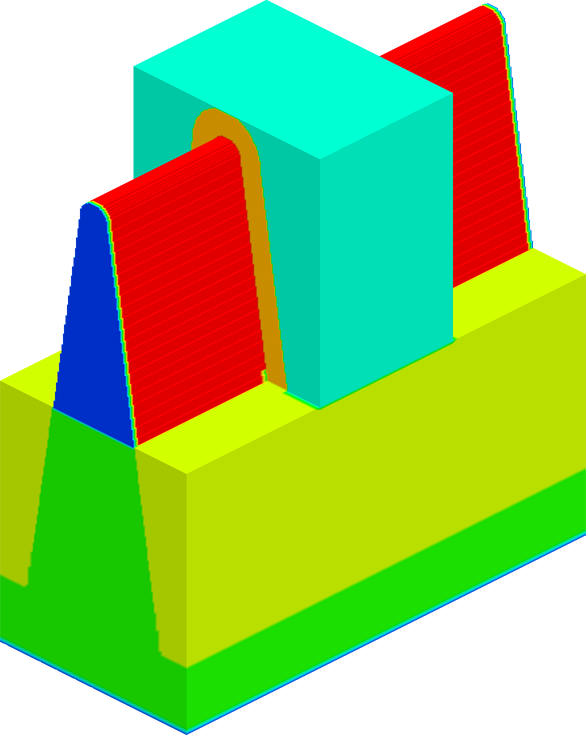

Mô phỏng hoạt động của trans 22nm.

GSS chạy một mô phỏng giả lập với hiệu điện thế cổng (Vg) dao động từ 0,0 - 0,9V. Tại các mức điện áp thấp, mật độ tập trung dòng điện (current density) nằm gần chính giữa "miếng vảy" và khi áp lên cao thì chúng dồn về phía đỉnh. Song điểm đáng lưu ý là sự xuất hiện của mật độ dòng về 2 "cạnh tam giác" và kéo dài xuống "cạnh đáy". Chi tiết này gợi lên giả thuyết liệu có phải chính nó đã gây ra hiện tượng rò dòng (leakage) vì mật độ dòng bị "thất thoát" về phía dưới hay không.

GSS cũng chạy một mô phỏng khác, nhưng dựa trên các trans "vuông" như trong lý thuyết của Intel. Theo so sánh của GSS: "Rõ ràng các vảy chữ nhật có hiệu ứng đoản kênh (short channel) tốt hơn (vảy tam giác). Song, vẫn còn câu hỏi trị giá cả triệu USD rằng liệu thiết kế vảy gần như tam giác là "do cố ý tạo ra", hay đấy là toàn bộ những gì mà công nghệ FinFET Bulk có thể đạt được?"

Ý nghĩa của câu hỏi trên nhằm bật lên một vấn đề đang nóng trong giới bán dẫn: liệu trans FinFET Bulk (kỹ thuật Intel và một số hãng có ý định dùng) có tốt hơn các trans Planar truyền thống? Một chi tiết rõ ràng là các chip SnB được sản xuất trên trans Planar dùng ít điện hơn chip IvB, mặc dù về bản chất kiến trúc chẳng khác nhau là mấy. Và trong trường hợp FinFET Bulk không tốt (lưu ý vẫn còn kỹ thuật FinFET SOI), việc làm ra những con chip nhỏ hơn nhưng tiết kiệm điện hơn trong tương lai sẽ gặp vấn đề rất lớn.

Tham khảo Chipworks & Gold Standard Simulations.