Samsung đã lên kế hoạch về chip 3nm, liệu chúng ta có thấy chip 1nm trong tương lai?

Về mặt kỹ thuật điều này là hoàn toàn có thể, nhưng các trở ngại về kinh tế có thể khiến những con chip này chỉ xuất hiện trong phòng thí nghiệm mà thôi.

Giữa tháng 5 vừa qua, Samsung cho biết đã đạt được bước đột phá trong việc chế tạo chip 3nm và đã gửi bộ kit về quá trình thiết kế chip đến các khách hàng tiềm năng. Như vậy, chỉ một thời gian ngắn sau khi chip 7nm trở nên phổ biến với các thiết bị di động, và khi chip 5nm vẫn còn chưa ra mắt, Samsung đã chuẩn bị ra mắt chip 3nm vào năm 2021.

Ngay vào thời điểm người ta tưởng chừng như Định luật Moore đã đi tới giới hạn, ngành công nghiệp vẫn giữ được nhịp độ tăng trưởng mạnh mẽ của mình. Nhưng khi chip 3nm đang chuẩn bị ra mắt và với nhịp độ thu nhỏ kích thước chip như hiện nay, liệu chúng ta có thể có các CPU dùng chip tiến trình 1nm hay không?

Nhưng có lẽ trước tiên chúng ta nên hiểu tiến trình chip là gì?

Tiến trình công nghệ chip, hay node tiến trình hay node, thường để chỉ một quy trình cụ thể để sản xuất bán dẫn và các quy tắc thiết kế của nó. Các tiến trình khác nhau (hay các node khác nhau) thường liên quan đến các thế hệ mạch và kiến trúc chip khác nhau. Thông thường, tiến trình công nghệ càng nhỏ có nghĩa là kích cỡ đặc trưng trên con chip (feature size) càng nhỏ, và càng tạo ra các bóng bán dẫn nhỏ hơn, có tốc độ nhanh hơn cũng như sử dụng năng lượng hiệu quả hơn.

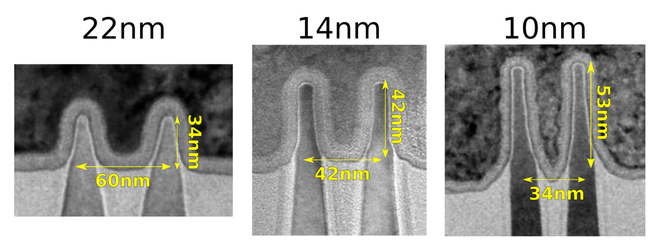

Trong lịch sử, tiến trình công nghệ thường có liên quan tới một số kích thước khác nhau trên bóng bán dẫn, bao gồm chiều dài cổng – khoảng cách giữa hai cực nguồn và cực máng trên bóng bán dẫn. Đây chính là nguồn gốc của các tiến trình với những cái tên như tiến trình 180nm, 110nm, 65nm hay 45nm. Số càng nhỏ, khoảng cách trên càng nhỏ, bóng bán dẫn càng nhỏ, chip càng nhanh hơn.

Nếu trước đây tên gọi tiến trình thường đại diện cho chiều dài cổng (khoảng cách từ cực source tới cực drain), giờ đây con số này chỉ còn mang ý nghĩa tên gọi, không phải kích thước cụ thể nào nữa.

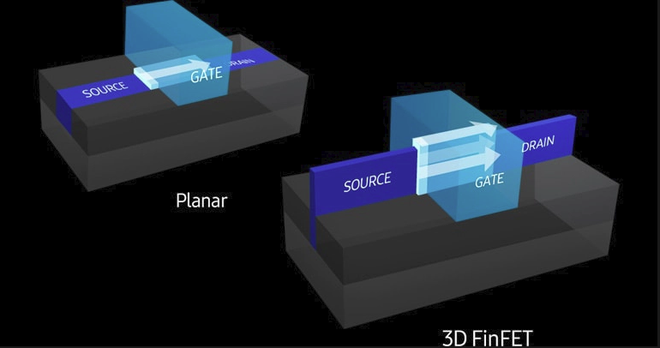

Tuy nhiên, bắt đầu từ tiến trình 45nm, Intel đã đưa chiều dài cổng đạt tới kích cỡ 25nm trên bóng bán dẫn dạng phẳng. Từ lúc này, việc thu hẹp hơn nữa khoảng cách này sẽ gây ra các hậu quả ngoài mong muốn. Cùng với việc Intel giới thiệu chip dạng FinFET từ tiến trình 22nm, trong khi các kích thước khác giảm đi, mật độ bóng bán dẫn vẫn tiếp tục tăng lên, chiều dài cổng gần như không đổi, thậm chí còn tăng lên.

Đến lúc này, tên gọi mỗi tiến trình dù vẫn là các kích thước tính theo nanomet, nhưng nó không còn biểu thị hay đại diện cho kích thước nào trên bóng bán dẫn nữa. Các con số như 16nm, 10nm hay 7nm chỉ còn có ý nghĩa là tên gọi của các tiến trình và tiếp thị cho năng lực của các nhà sản xuất chip nhiều hơn một kích thước thực sự nào đó.

Vậy chip tiến trình 1nm có thể đến trong tương lai?

Với việc các cái tên như tiến trình 10nm, 7nm hay 3nm chỉ còn mang ý nghĩa tên gọi, thay vì là một kích thước thực tế nào đó của bóng bán dẫn, vì vậy về mặt lý thuyết kỹ thuật, các chip tiến trình 1nm là điều hoàn toàn có thể.

Đặc biệt, lộ trình của những tiến trình chip dưới 3nm còn được mô tả trong Lộ trình công nghệ Quốc tế về bán dẫn ITRS phiên bản 2.0 – bộ tài liệu được các chuyên gia hàng đầu trong ngành bán dẫn tạo nên. Theo phiên bản mới nhất của bộ tài liệu này, những tiến trình nhỏ hơn 3nm sẽ là 2,5nm và 1,5nm, dự kiến sẽ ra mắt vào những năm 2027 và 2030. Tuy nhiên tất cả vẫn chỉ là các dự đoán, do vẫn còn các trở ngại khác về mặt kỹ thuật.

Với chip FinFET, nỗ lực của các nhà sản xuất tập trung vào việc thu hẹp khoảng cách giữa các fin (fin pitch), độ rộng của mỗi fin (fin width) và gia tăng chiều cao của chúng (fin height).

Một điều cần chú ý rằng, trong khi chiều dài cổng không còn thu hẹp được nữa, các kích thước khác của bóng bán dẫn vẫn tiếp tục được thu hẹp. Với các chip dạng FinFET, những nhà sản xuất bán dẫn tập trung vào việc thu hẹp chân đế của mỗi fin (hay vây chip), khoảng cách giữa chúng và làm chúng cao hơn. Mục đích cuối cùng vẫn là thu hẹp kích thước bóng bán dẫn.

Tuy nhiên, đến các tiến trình hiện tại, những công nghệ chế tạo chip đã cho thấy sự hụt hơi của mình. Từ khi chuyển sang các chip 22nm/20nm, các nhà sản xuất bán dẫn đã sử dụng kỹ thuật quang khắc nhúng 193nm (193nm immersion lithography), tuy nhiên kỹ thuật này đã đạt đến giới hạn của mình khi chỉ có thể tạo ra các đường khắc có kích thước 40nm trở lên, vì vậy nhiều nhà sản xuất chip đang chuyển sang kỹ thuật khác khi hướng tới chip có tiến trình nhỏ hơn nữa.

Để sử dụng tia EUV chế tạo chip, cần có môi trường chân không gần tuyệt đối, do vậy các cỗ máy chế tạo chip như trên của ASML trở nên rất cần thiết với các nhà sản xuất chip.

Đó là lý do hàng loạt nhà sản xuất chip dù vẫn dùng quang khắc 193nm để sản xuất chip 10nm, như Intel và TSMC, hiện đều đã bắt đầu chuyển sang sử dụng kỹ thuật siêu tia cực tím EUV, với khả năng tạo ra các đường khắc có kích thước chỉ 13,5nm, để sản xuất các chip 10nm với chất lượng tốt hơn.

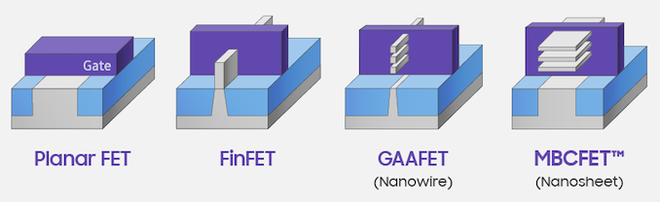

Chuyển sang các tiến trình thấp hơn có thể sẽ cần đến các thiết kế chip mới thay thế cho FinFET, như GAAFET và sau đó là MBCFET.

Tuy nhiên, kỹ thuật quang khắc EUV cũng có thể chỉ phù hợp đến các tiến trình 7nm và 5nm, xuống đến các tiến trình nhỏ hơn 3nm, các nhà sản xuất chip sẽ cần đến công nghệ quang khắc EUV thế hệ mới có tên EUV khẩu độ cao (High-Numerical Aperture EUV). Không chỉ vậy, tại các tiến trình nhỏ này, chip dạng FinFET sẽ không còn phù hợp nữa mà có thể phải thay thế bằng dạng GAAFETs để gia tăng số lượng bóng bán dẫn.

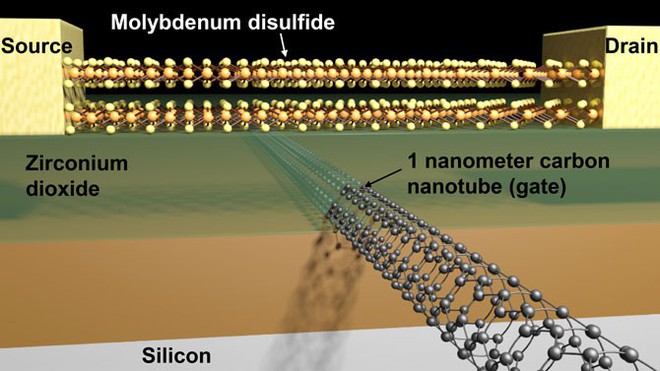

Tuy nhiên, trên đây chỉ là các thách thức về mặt kỹ thuật trong việc sản xuất hàng loạt chip, còn đối với việc sản xuất trong phòng thí nghiệm, năm 2016, các nhà nghiên cứu tại phòng thí nghiệm Lawrence Berkeley Lab còn tạo nên được bóng bán dẫn với chiều dài chỉ 1nm – nhỏ hơn rất nhiều so với kích thước chip theo lộ trình của ITRS. Tuy nhiên, các nhà nghiên cứu sử dụng các vật liệu mới như ống nano carbon và hợp chất Molybden di-Sulfide, do vậy sẽ mất rất nhiều thời gian nếu đi vào sản xuất hàng loạt.

Bóng bán dẫn có chiều dài 1nm đã xuất hiện trong phòng thí nghiệm, tuy nhiên để ra mắt một con chip với bóng bán dẫn như vậy sẽ cần rất nhiều thời gian nữa.

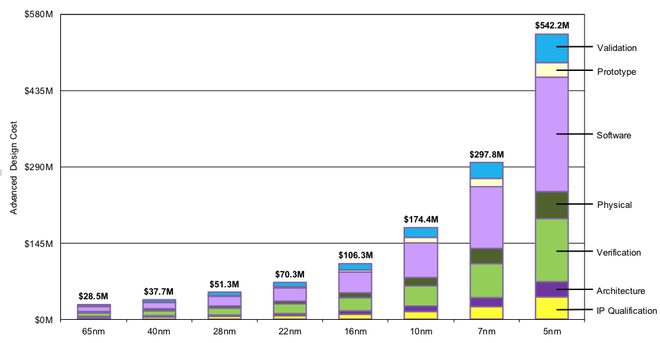

Không chỉ các thách thức kỹ thuật, một rào cản khác có thể ngăn cản những bộ xử lý tiến trình 1nm ra mắt trên thực tế là yếu tố kinh tế. Chi phí phát triển những con chip với các tiến trình nhỏ hẹp hơn đã tăng vọt trong thời gian gần đây, và do đó hiện nay chỉ còn những công ty lớn mới có đủ khả năng thiết kế chip trên các tiến trình này, như Intel, AMD, Qualcomm hay Apple, Samsung.

Dự kiến chi phí phát triển chip 5nm sẽ cao gần gấp đôi chip 7nm và cao gấp 3 lần chip 10nm.

Trong khi chi phí phát triển chip đang tăng phi mã như hiện nay, còn chi phí sản xuất chế tạo chip cũng tăng theo mỗi khi chuyển sang một tiến trình mới, có thể đến một lúc nào đó, ngay cả Intel cũng dừng tạo ra các bóng bán dẫn nhỏ hơn nữa. Do vậy, nhiều người dự đoán rằng, 3nm có thể sẽ là giới hạn cuối của quá trình này.

Tuy nhiên, với lộ trình của ITRS đặt ra cho các tiến trình 2,5nm và 1,5nm vào những năm 2027 và 2030, có lẽ chúng ta còn phải chờ rất lâu nữa mới giải đáp được các thắc mắc trên về giới hạn của định luật Moore.

NỔI BẬT TRANG CHỦ

-

Chính thức ra mắt OPPO Find N6 tại Việt Nam: Nếp gấp "vô hình", Snapdragon 8 Elite Gen 5, tích hợp bút Magic AI và giá bán 64.99 triệu Đồng

Sau thời gian ra mắt tại thị trường quốc tế, OPPO Find N6 đã chính thức được giới thiệu tại Việt Nam.

-

Điện thoại này của Xiaomi vừa ra mắt được 1 ngày đã bán hơn 1.000 máy: Chuyện gì đang xảy ra vậy?