Tại sao các nhà sản xuất chip không tăng kích thước chip để tăng số lượng transistor mà phải tìm mọi cách để thu hẹp chip?

Không chỉ vì các nguyên nhân từ hiệu năng và hiệu quả năng lượng, nỗ lực thu hẹp kích thước chip còn đem lại các lợi thế vượt trội về tính kinh tế, cho dù đánh đổi lại là những khoản đầu tư khổng lồ về công nghệ sản xuất.

*Lược dịch câu trả lời của Luc Boulesteix với sự đồng thuận của Sebastian Dadeby, thạc sĩ khoa học ngành Thiết kế hệ thống và Kỹ sư điện, Đại học công nghệ Chalmers.

Rõ ràng việc thu hẹp tiến trình sản xuất chip để gia tăng số lượng và mật độ bóng bán dẫn là việc ngày càng khó khăn và tốn kém, vậy tại sao các công ty sản xuất chip không xây dựng các die chip (hay các đế chip) để gia tăng số lượng bóng bán dẫn, thay vì phải vất vả tìm cách thu hẹp tiến trình và kích thước die chip?

Tuy nhiên, câu hỏi chính xác nhất cho điều này nên là, tăng kích thước die chip để làm gì?

Các nhà sản xuất hoàn toàn có thể làm các chip với kích thước lớn hơn, nhưng có lẽ nó sẽ chẳng mang lại nhiều ý nghĩa. Nguyên nhân đơn giản của việc này là vì người ta cần đặt con chip vào vừa trong thiết bị, một con chip mạnh mẽ sẽ trở nên vô nghĩa nếu nó không thể đặt vừa trong thiết bị cần dùng.

Dưới đây là hình ảnh của chip GV100, GPU do Nvidia thiết kế. Nó có đầy sức mạnh và có diện tích lên tới 852mm2. Liệu bạn có thể đặt nó vào trong chiếc smartwatch không?

GPU Quadro GV100 của Nvidia.

Tuy nhiên, chắc chắn những con chip kích thước lớn như thế này sẽ có chỗ trong các máy tính desktop hoặc máy chủ, vốn ít quan tâm đến các giới hạn về kích thước. Nếu nhìn vào các con chip dành cho máy chủ hoặc siêu chip HEDT (High-End Desktop), bạn sẽ thấy các die chip này càng ngày càng rộng hơn, lớn hơn để chứa nhiều nhân xử lý hơn.

Ngay cả như vậy, vẫn có một giới hạn thực tế cho kích thước tối đa của các con chip này, không chỉ vì để có thể đặt vừa trong thiết bị của mình mà đó còn là kích thước thực tế chúng ta có thể sản xuất.

Các giới hạn trong sản xuất chip

Đầu tiên, các micro chip đều được cắt ra từ các tấm bán dẫn lớn hơn được gọi là các đĩa wafer. Đó là các đĩa silicon hình tròn có đường kính 300mm như bạn thường thấy ngày nay. Và rõ ràng đó không phải là những chiếc đĩa có kích thước vô hạn.

Điều này có nghĩa là các nhà sản xuất có thể thu được nhiều chip hơn trên một đĩa wafer này nếu kích thước của mỗi con chip giảm xuống. Ngược lại, số lượng chip trên mỗi đĩa wafer sẽ giảm đi nếu kích thước của chúng tăng lên. Và điều này cũng đúng nếu ta tăng kích thước die chip lên, die chip lớn hơn tương đương với số lượng chip trên mỗi đĩa wafer ít hơn, và ngược lại.

Các loại đĩa wafer với các kích thước khác nhau.

Ngành sản xuất bán dẫn là một ngành có độ chính xác khắt khe đến mức đáng kinh ngạc, nhưng nó vẫn không hoàn hảo. Không phải toàn bộ các die chip được khắc trên đĩa wafer đều có thể sử dụng được, khi một số khuyết tật có thể xuất hiện ngẫu nhiên trên các đĩa đó (ví dụ một vài hạt bụi hoặc vết bẩn nào đó).

Bất kỳ con chip nào được xây dựng trên tại vị trí bị khuyết tật đó đều được xem như hỏng hoàn toàn và không thể sửa chữa được. Điều này luôn có thể xảy ra cho dù con chip đó có kích thước lớn hay nhỏ. Và đây là một vấn đề trong việc xác định chi phí sản xuất cho mỗi con chip.

Trong khi chi phí cho nguyên vật liệu cho mỗi con chip tương đồng với kích thước die chip – die chip càng lớn thì kích thước càng tăng – nhưng số lượng thực sự các chip có thể hoạt động trên một đĩa wafer lại không hoàn toàn như vậy.

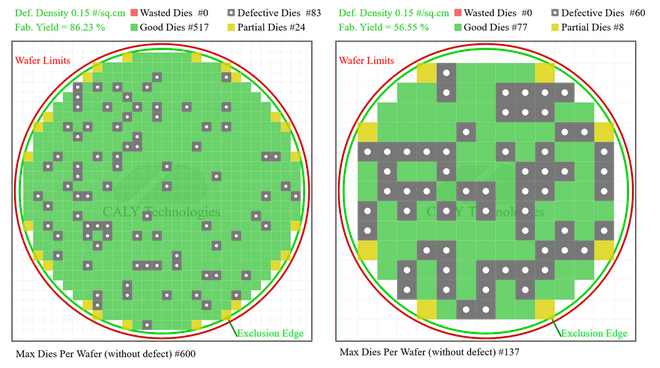

Chi phí cho mỗi đĩa wafer là cố định, vì vậy số lượng chip có thể hoạt động ít hơn nghĩa là chi phí trên mỗi chip cũng cao hơn, kéo theo chi phí sản xuất cho mỗi chip này cũng tăng lên theo. Thử so sánh năng suất sản xuất giữa các die chip diện tích 100mm2 và 400mm2 trên một đĩa wafer 300mm (giả sử cả hai đều có mật độ khuyết tật là 0,15 khuyết tật trên mỗi cm2) như hình vẽ dưới đây.

So sánh số lượng chip nguyên vẹn thu được trên mỗi đĩa wafer

Bạn sẽ thấy tỷ lệ các chip hoạt động với các chip chết giữa hai loại die chip không giống nhau. Dù cùng một tỷ lệ khuyết tật, nhưng số lượng chip chết trên die chip 400mm2 nhiều hơn so với die chip 100mm2.

Nếu chúng ta giả sử mỗi đĩa wafer sẽ có giá khoảng 10.000 USD, vì vậy chúng ta sẽ có chi phí cho mỗi chip vào khoảng 19,34 USD cho mỗi chip die 100mm2 và vào khoảng 129,87 USD cho mỗi chip die 400mm2. Nghĩa là khi bạn tăng kích thước die chip lên 4 lần, chi phí cho mỗi chip tăng lên gấp hơn 6,71 lần. Chênh lệch này còn lớn hơn nữa khi bạn tăng diện tích chip lên: ví dụ với diện tích die chip là 625mm2, chi phí cho mỗi chip sẽ vào khoảng 294,1 USD, nghĩa là chi phí cao gấp hơn 15,2 lần cho việc tăng diện tích lên thêm 6,25 lần.

Đây chính là giới hạn thực tế của việc sản xuất các chip có kích thước lớn: chi phí sẽ gia tăng theo cấp số nhân so với việc tăng diện tích die chip. Không có cách nào có thể tạo ra các con chip lớn hơn trong khi vẫn giữ được tính kinh tế.

Năng lượng và các hạn chế về thiết kế

Tăng cường thêm mật độ bóng bán dẫn không phải là nguyên nhân duy nhất cho việc các nhà sản xuất liên tục tìm cách chuyển sang các tiến trình nhỏ hơn: bên cạnh nhiều ưu điểm khác, các bóng bán dẫn nhỏ hơn sẽ sử dụng ít năng lượng hơn.

Trong khi một con chip lớn hơn dù có nhiều bóng bán dẫn hơn, nhưng lại không làm các bóng bán dẫn đó có hiệu quả năng lượng cao hơn. Bạn vẫn có thể tích hợp thêm một số tính năng lên die chip kích thước lớn đó, nhưng mức tiêu thụ năng lượng trên mỗi bóng bán dẫn vẫn sẽ giữ nguyên, với cùng tần số và điện thế.

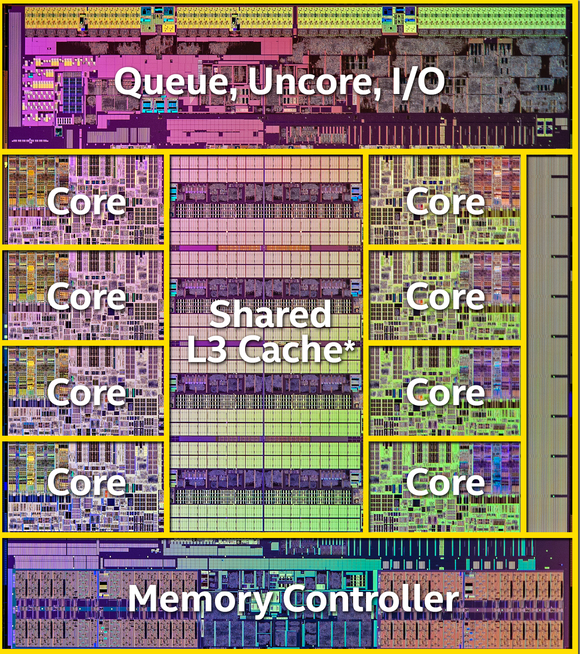

Die chip của Intel Core i7-5960X với 8 lõi 16 luồng ra mắt năm 2014.

Điều đó sẽ kéo theo một giới hạn khác: đó là về điện năng tiêu thụ của mỗi thiết bị. Đối với các máy tính desktop, điện năng tiêu thụ cao sẽ cần có thêm các bộ phận tản nhiệt và làm mát. Còn đối với các thiết bị di động, giới hạn về điện năng sẽ càng trở nên quan trọng hơn khi chúng đều chạy bằng pin.

Để đảm bảo thời lượng pin đối với các con chip lớn hơn, bạn sẽ cần giảm điện thế hoạt động và xung nhịp của nó xuống. Tất nhiên điều này cũng làm mất đi một số lợi thế về hiệu năng gia tăng dựa trên việc gia tăng số lượng bóng bán dẫn.

Hơn nữa đối với các nhà thiết kế chip, việc gia tăng kích thước thực sự là một cơn ác mộng: các tín hiệu điện chỉ có một tốc độ giới hạn khi di chuyển từ dây nối sang vật liệu bán dẫn. Nếu bạn gia tăng kích thước chip, cũng có nghĩa sẽ làm gia tăng khoảng cách một tín hiệu cần phải di chuyển để tới được các bộ phận chức năng khác.

Với hàng kilomet dây dẫn bên trong mỗi con chip hiện đại, khi tăng khoảng cách di chuyển của tín hiệu, mọi thứ sẽ trở nên phức tạp rất nhanh. Sử dụng tất cả các bóng bán dẫn một cách hiệu quả sẽ trở thành một thách thức đáng kể khi ta nới rộng các khoảng cách đó lên.

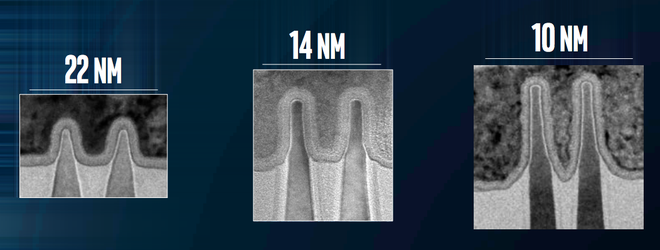

Bắt đầu từ tiến trình 22nm, thay vì thu hẹp kênh dẫn giữa các cực trên bóng bán dẫn, các nhà sản xuất chuyển chọn cách nâng cao các cực source và drain trên chip và thu hẹp khoảng cách giữa chúng, nhằm giảm kích thước bóng bán dẫn và gia tăng mật độ của chúng trên chip.

Thêm vào đó, việc gia tăng kích thước chip còn kéo theo nhiều vấn đề khác: làm sao bạn có thể đồng bộ một xung tín hiệu (một clock signal) khi nó không thể truyền qua con chip trong một chu kỳ xung nhịp đó. Làm thế nào bạn có thể truyền một rãnh năng lượng thông qua đó? Nếu bạn không chú ý đến vấn đề này, một số khu vực trong con chip có thể bị mất điện cục bộ nếu tải công việc thay đổi đột ngột.

Khi không thể xây dựng các con chip lớn hơn để tăng cường hiệu năng, các nhà sản xuất không còn cách nào khác ngoài việc chạy đua thu hẹp tiến trình chip. Khi số lượng bóng bán dẫn và khoảng cách giữa chúng trên chip phẳng đã không thể gia tăng được nữa, các nhà sản xuất đã chuyển sang phương pháp tích hợp hàng dọc với các thiết kế 2,5D và 3D FinFET.

Dù chúng không thể giải quyết toàn bộ các vấn đề liên quan đến phương pháp tích hợp hàng ngang, nhưng nó vẫn mang tới một số ưu điểm quan trọng, bao gồm thu hẹp kích thước die chip và giảm đáng kể chi phí.

NỔI BẬT TRANG CHỦ

-

MacBook Neo cuối cùng đã mở đặt trước tại Việt Nam: Giá rẻ nhất lịch sử, sinh viên mua còn rẻ hơn tới vài triệu

MacBook Neo dùng chip A18 Pro từ iPhone 16 Pro, pin tới 16 giờ, nặng 1,23 kg. Tại Việt Nam, máy có giá từ 16.490.000 đồng, mở bán từ ngày 10/4.

-

POCO X8 Pro Max: Chiếc máy 13 triệu đang làm khó cả phân khúc flagship!