Không có máy quang khắc EUV, tại sao SMIC sản xuất được chip 7nm?

Trước SMIC, TSMC và Samsung đều đã sản xuất được chip 7nm dù không có máy quang khắc EUV.

Một báo cáo mới đây của trang TechInsights cho thấy nỗ lực đáng kinh ngạc của hãng đúc chip Trung Quốc SMIC. Dù không được tiếp cận với các máy quang khắc EUV hiện đại của hãng ASML, nhưng công ty Trung Quốc vẫn làm được các chip 7nm và cung cấp cho một công ty thiết kế bộ xử lý khai thác Bitcoin.

Nhưng làm thế nào hãng đúc chip Trung Quốc SMIC có thể làm được điều này trong khi họ không thể mua được các cỗ máy quang khắc chip EUV của ASML?

Trên thực tế, các cỗ máy quang khắc EUV của ASML không phải là lựa chọn duy nhất để sản xuất được các chip 7nm. Trước khi những cỗ máy này xuất hiện, các hãng đúc chip hàng đầu thế giới bao gồm TSMC và Samsung đều đã sản xuất được chip 7nm bằng các máy quang khắc dùng công nghệ cũ hơn.

Họ làm điều đó như thế nào?

Nhiều năm trước khi các máy quang khắc EUV của ASML ra mắt, các hãng đúc chip vẫn phải sử dụng dòng máy quang khắc dùng ánh sáng với bước sóng 193nm – lớn hơn nhiều so với các đường rãnh cần khắc trên mỗi con chip. Nhưng khi tiến trình của các con chip tiến gần đến 80nm – giới hạn của hệ thống quang khắc này – các nhà sản xuất chip đã tìm ra nhiều giải pháp khác nhau để tận dụng hệ thống này cho việc thu nhỏ bóng bán dẫn, "câu giờ" cho đến khi các dòng máy quang khắc EUV hiện đại hơn xuất hiện.

Đầu tiên là Immersion Lithography (kỹ thuật quang khắc nhúng), trong đó phần không khí thông thường nằm giữa ống kính đến tấm wafer được thay thế bằng một chất lỏng có hệ số chiết xuất cao hơn một – cho phép giảm độ phân giải của ánh sáng để có thể tạo ra các chip có tiến trình đến 45nm hoặc nhỏ hơn nữa.

Nhưng từ tiến trình nhỏ hơn 22nm, các nhà sản xuất chip lại một lần nữa gặp phải rào cản mới. Mật độ bóng bán dẫn quá dày của tiến trình này làm cho việc quang khắc không thể tạo ra các đường nét đủ chính xác chỉ trong một lần in.

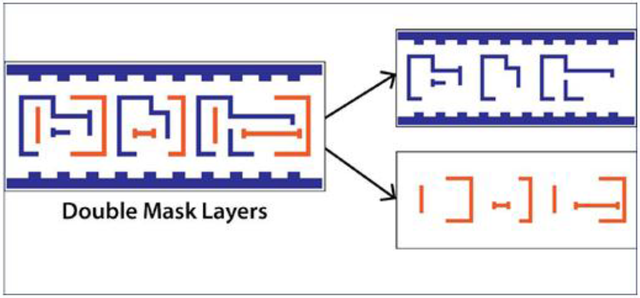

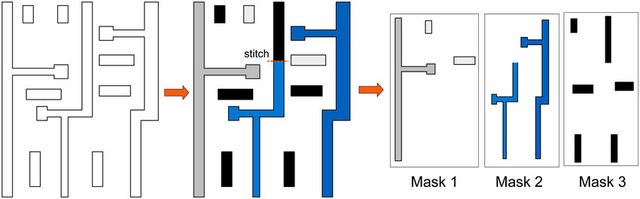

Một lớp mẫu hình chip giờ sẽ phải tách thành 2 mẫu hình khác nhau để có thể in được bằng máy quang khắc DUV.

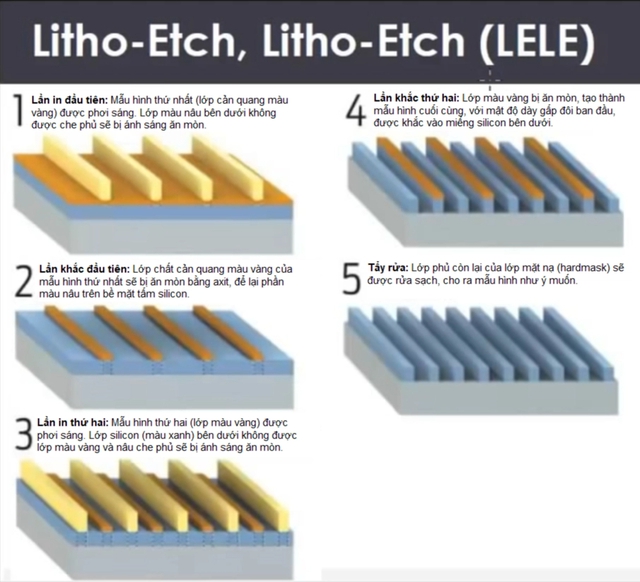

Để cải thiện chất lượng các đường rãnh trên tấm wafer, các nhà sản xuất chip tìm đến giải pháp quang khắc mẫu hình kép hay còn gọi double patterning lithography. Quá trình quang khắc chip giờ được chia thành 4 bước chính: Litho-etch-litho-etch (in – khắc – in – khắc) hay LELE.

Với giải pháp này, mỗi lớp mẫu hình của con chip, thay vì được in trong một lần duy nhất như trước, sẽ được chia thành 2 lớp bố cục với mật độ bóng bán dẫn thấp hơn. Sau đó, 2 lớp bố cục này sẽ lần lượt được tạo thành từ hai quá trình in và khắc riêng biệt để tạo thành 2 mẫu hình thô. Tiếp đến, chúng lại được kết hợp lại và xếp chồng lên nhau để tạo thành một mẫu hình có đường khắc mịn hơn và khoảng cách hẹp hơn trên tấm wafer.

Từ giải pháp quang khắc đa mẫu hình, các nhà sản xuất chip phát triển nên các kỹ thuật tinh chỉnh, cắt gọt bề mặt chất bán dẫn bằng các lớp chất cản quang cũng như ăn mòn, kết hợp với quang khắc để tạo nên các mẫu hình như ý muốn – hay còn gọi là self-aligned double patterning (SADP) và self-aligned quadruple patterning (SAQP).

Quy trình quang khắc chip SAQP thu nhỏ mẫu hình từ 80nm xuống 20nm: In mẫu hình thứ nhất - khắc tạo đường trục phía trên - phủ lớp chất đệm 1 - khắc ăn mòn lớp chất đệm 1 - loại bỏ phần trục phía trên - khắc ăn mòn tạo đường trục dưới - phủ lớp chất đệm 2 - khắc mài mòn lớp chất đệm 2 - loại bỏ đường trục dưới - khắc ăn mòn vào lớp hardmask

Một phần quan trọng khác phải kể đến là các phần mềm thiết kế chip khi chúng giúp các nhà sản xuất chip phân tách các mẫu hình ban đầu thành các lớp mẫu hình tối ưu cho quá trình quang khắc.

Đồng thời với giải pháp quang khắc đa mẫu hình để vượt qua giới hạn của bước sóng ánh sáng, từ các tiến trình 45nm, các nhà sản xuất chip bắt đầu chuyển từ thiết kế chip phẳng sang chip ba chiều với FinFET. Điều này giúp các nhà sản xuất chip có thể tiếp tục gia tăng mật độ bóng bán dẫn mà không phải thu nhỏ quá mức khoảng cách trong các bóng bán dẫn.

Một thiết kế bóng bán dẫn dạng FinFET

Với giải pháp quang khắc mẫu hình kép, các nhà sản xuất chip có thể giảm tiến trình công nghệ trên bóng bán dẫn đi 30% nữa (từ 40nm xuống còn 14nm). Nhưng khi tiến trình công nghệ chip tiến gần đến 10nm và thấp hơn nữa, ví dụ 7nm, mà dòng máy quang khắc EUV vẫn chưa ra mắt, các nhà sản xuất chip lại phải tiếp tục tận dụng dòng máy cũ bằng giải pháp sản xuất mới.

Lần này, các nhà sản xuất bán dẫn còn dùng đến giải pháp quang khắc 3 mẫu hình (Triple Patterning). Các công đoạn sản xuất chip kéo dài hơn nữa với 3 lần in-khắc (LELELE) cho mỗi lớp mẫu hình. Quá trình sản xuất chip vốn đã phức tạp với giải pháp mẫu hình kép, giờ lại càng trở nên phức tạp gấp bội với quang khắc 3 mẫu hình.

Với triple patterning, mỗi lớp mẫu hình sẽ được tách thành 3 mẫu hình khác nhau để lần lượt in-khắc chúng lên bề mặt chất bán dẫn.

Các thiết kế chip phải chỉnh sửa lại, các công cụ phần mềm cho sản xuất chip cũng phải thiết kế lại. Việc phân tách một thiết kế chip ban đầu thành 3 mẫu hình tối ưu trở nên khó khăn hơn nhiều so với tách thành 2 mẫu hình. Nhưng quan trọng hơn cả là công đoạn sản xuất chip trở nên phức tạp và kéo dài hơn nhiều trước đây.

Mặc dù vậy, giải pháp này đã giúp các nhà sản xuất chip như TSMC và Samsung trở thành các công ty đầu tiên sản xuất được chip 7nm bằng máy quang khắc DUV, với chip A12 Bionic của Apple ra mắt năm 2018 chính là dòng bộ xử lý đầu tiên ứng dụng quy trình chip 7nm của TSMC. Do vậy, không lạ khi giờ đây SMIC có thể sản xuất được chip 7nm dù không có máy quang khắc EUV của ASML.

Cái giá phải trả không hề nhỏ

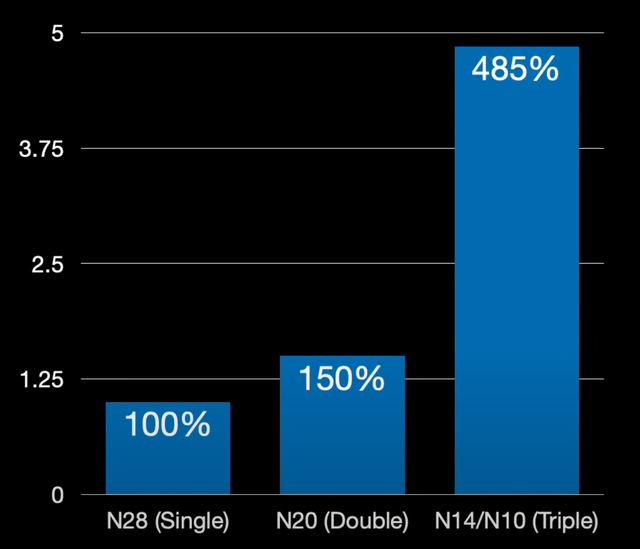

Với tiến trình 45/40nm, thiết kế của mỗi con chip được chia thành 40 lớp mặt nạ (lớp mask) khác nhau. Còn với tiến trình 14nm và 10nm, số lượng mặt nạ chip lên đến 60 lớp. Thậm chí với tiến trình 7nm, số lượng mặt nạ cho mỗi thiết kế chip có thể lên đến con số 80 hoặc 85 lớp. Số lượng lớp mặt nạ nhiều hơn nghĩa là chi phí sẽ bị đội lên.

Thêm vào đó, thời gian sản xuất chip cũng kéo dài hơn. Nếu trước đây, chỉ mất từ 1 đến 1,5 ngày để xử lý một lớp mặt nạ, còn với quang khắc đa mẫu hình ở 7nm, các nhà sản xuất chip mất đến 5 tháng để xuất xưởng các tấm wafer hoàn thiện.

Chi phí sản xuất tăng vọt mỗi khi tiến trình được thu nhỏ hơn.

Vấn đề không chỉ có vậy, số lượng mặt nạ tăng lên, kéo theo số lượng lớp phủ lên bề mặt tấm wafer. Càng nhiều lớp phủ, càng khó căn chỉnh các cực bóng bán dẫn trong quá trình sản xuất. Điều này càng khiến quá trình sản xuất chip gặp nhiều lỗi hơn.

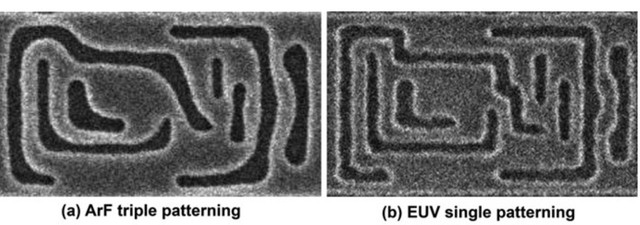

Tất cả các yếu tố trên cho thấy bước ngoặt khổng lồ mà máy quang khắc EUV của ASML mang lại cho ngành công nghiệp chip. Với bước sóng rất ngắn, chỉ 13,5nm, ngắn hơn nhiều so với bước sóng 193nm của máy quang khắc DUV, máy quang khắc EUV giải quyết hàng loạt vấn đề mà ngành công nghiệp chip đang gặp phải.

Chất lượng mẫu hình sản xuất bằng in 3 mẫu hình (trái) kém hơn hẳn so với mẫu hình sản xuất bằng máy EUV chỉ trong một lần in (phải).

Bước sóng ngắn hơn giúp cỗ máy của ASML có thể quang khắc chip với số lớp mẫu hình ít hơn nhưng vẫn mang lại chất lượng tốt hơn – ngay cả khi tiến trình chip được giảm xuống 5nm. Số lượng mẫu hình ít hơn giúp giảm chi phí và thời gian sản xuất chip, đồng thời giảm tỷ lệ chip lỗi cũng như gia tăng năng suất sản xuất chip.

Nhưng SMIC lại không được hưởng thành quả cuộc cách mạng này. Không tiếp cận được các máy quang khắc EUV cao cấp, họ vẫn phải dựa vào các máy quang khắc DUV thế hệ cũ để có thể sản xuất được chip 7nm – dù chúng có mức độ phức tạp, chi phí cao và năng suất thấp hơn nhiều so với việc sản xuất các chip có tiến trình lớn hơn.

Điều này có thể giải thích lý do vì sao, các chip 7nm của SMIC mới chỉ được ứng dụng cho bộ xử lý của máy tính khai thác Bitcoin. Các chip khai thác Bitcoin này đơn giản hơn cũng như chỉ được ứng dụng trong một lĩnh vực không quá quan trọng. Trong khi đó, người khổng lồ công nghệ Trung Quốc Huawei, dù đang khao khát các chip công nghệ cao hơn bao giờ hết, vẫn chưa cho thấy động thái sẽ sử dụng sản phẩm của SMIC.

NỔI BẬT TRANG CHỦ

-

Apple kỷ niệm 50 năm: Từ Apple II đến Vision Pro, hành trình "Think Different" đã thay đổi cả ngành công nghệ

Apple kỷ niệm 50 năm thành lập, nhìn lại hành trình đổi mới công nghệ và triết lý "Think Different" đã định hình nhiều sản phẩm biểu tượng.

-

Dân mạng truyền nhau tấm ảnh S26 Ultra vừa bán đã dính "sọc màn hình", sự thật thế nào?